1.DSP芯片發展

隨著DSP芯片應用領域的不斷擴大,DSP芯片已形成低、中、高三個檔次:低端產品執行速度一般為20~50MIPS,能維持適量存儲和功耗,提供了較好的性能價格比,適用于儀器儀表和精密控制等;中端產品執行速度一般為100 ~150MIPS,結構較為復雜,具有較高的處理速度和低的功耗,適用于無線電信設備和高速解調器等;高端產品執行速度一般為1O00MIPS 以上,處理速度很高,產品結構多樣化,適用于圖像技術和智能通信基站等。

對于種類繁多的DSP芯片,一般可按其工作的數據格式將其分為兩大類定點DSP芯片和浮點DSP芯片。定點DSP品種最多,處理速度為20 ~240OMIPS;浮點DSP處理速度為40M ~ 1GFLOPS。

圖1 DSP芯片

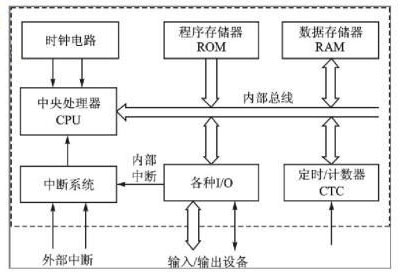

2.DSP芯片結構

DSP芯片是專為高速信號處理而設計的,由于采用了不同于普通單片機的體系結構,因而具有一些顯著的特點。

2.1哈佛結構

傳統的馮諾伊曼( Von-Neumann)結構由于具有單一公用的數據和指令總線,因此在高速運算時,往往在傳輸通道上會出現瓶頸效應。DSP芯片內部一般采用哈佛(Harvard)結構,片內至少有四套總線:程序的數據總線與地址總線,數據的數據總線與地址總線。這種分離的程序總線和數據總線,可允許在一個機器周期內同時獲取指令字(來自程序存儲器)和操作數(來自數據存儲器),從而提高了執行速度。

2.2硬件乘法器

數字信號處理中最重要的一個基本運算是乘法累加運算,也是最主要和最耗時的運算,因此單周期的硬件乘法器是 DSP芯片實現快速運算的保證。現代高性能的DSP芯片甚至具有兩個以上的硬件乘法器用以提高運算速度。數據寬度也從16位增加到32位。

2.3多個并行處理單元

DSP內部一般都集成了多個處理單元,如硬件乘法器(MUL)、累加器(ACC)、算術邏輯單元(ALU)、輔助算術單元(ARAU)以及 DMA控制器等。它們都可以并行地在同一個周期內執行不同的任務,例如輔助算術單元能為下一次的運算做好準備,適合于完成連續的乘加運算。芯片內部還包括有其他總線,如 DMA總線等,可實現數據的后臺傳輸而幾乎不影響主 CPU的性能的有FFT的位反轉尋址,語音的A律、p律算法等。

為了提高并行處理能力,現代DSP芯片通常采用單指令多數據流結構(SIMD)、超長指令字結構(VLIW)、超標量體系結構、多DSP核體系結構和DSP/MCU混合結構,這些并行處理機制大大提高了DSP芯片的性能。

2.4流水線技術

DSP芯片的哈佛結構為流水線技術提供了方便。由于采用流水線技術,DSP芯片可以單周期完成乘沃累加運算,大大提高了運算速度。而DSP芯片的指令基本上都是單周期指令,因此單周期指令執行時間可以作為衡量DSP芯片性能的一個主要指標。

2.5片上存儲器

外部存儲器一般不能適應高性能DSP核的處理速度,因此在片上設置較大的程序/數據存儲器以減少對外部存儲器中程序/數據的訪問次數,充分發揮DSP核的高性能。目前高性能DSP芯片上的可配置程度/數據RAM高達7MB。采用大的片子存儲器可以減少外部存儲器接口的引腳,甚至省略外部存儲器接口,而且也減小了芯片的封裝體積。

2.6多種外設和接口

為了加強 DSP芯片的通用性,DSP芯片上增加了許多外設。可能包括的外設有:多路DMA通道、外部主機接口、外部存儲器接口、芯片間高速鏈接口、外部中斷、通信串口、定時器、可編程鎖相環、A/D轉換器、JTAG接口等。

2.7特殊尋址模式

為了滿足FFT積等數字信號處理的特殊要求,DSP芯片大多包含專門的硬件地址產生器,用以實現循環尋址和位翻轉尋址,并在軟件上設置了相應的指令。

2.8零消耗循環控制

數字信號處理的一大特點是大部分處理時間花在了較小循環的少量核心代碼上。大部分DSP芯片具有零消耗循環控制的專門硬件,可以省去循環計數器的測試指令,從而提高了代碼效率,減少了執行時間。

2.9JTAG接口

由于DSP芯片結構的復雜化、工作速度的提高、外部引腳的增多、封裝面積減小而導致的引腳排列密集等原因,傳統的并行仿真方式已不適合于DSP芯片的發展和應用開發。1991年公布的JTAG接口標準滿足了IC制造商和用戶的要求,1993年 JTAG接口標準修訂為5線接口。在片JTAG接口為 DSP芯片的測試和仿真提供了很大的便利。

2.10程序的加載引導

加載引導是指器件在上電復位后執行一段引導程序,用于從端口(異步串口、I/O口、主機接口)或外部EPROM/FLASH存儲器中加載程序至高速RAM中運行。一般用 EPROM/FLASH存儲器存儲程序,但是其訪問速度較慢,而一些已有的高速EPROM/FLASH存儲器價格昂貴且容量有限;同時高速大容量靜態RAM價格又在不斷下降,因此這種加載方式是一個有效的性價比解決方法。

3.在圖像技術中的應用

目前實現圖像處理的主要方式有四種:①基于通用PC微機;②基于通用DSP芯片;③基于專用DSP芯片;④基于可編程FPGA。在通用PC微機上主要是軟件實現圖像處理,能夠提供中等的圖像處理能力,但是要占用CPU幾乎全部的處理能力。在獨立機型設計中一般采用其他三種方式:①基于可編程FPGA的設計比較復雜而且難度較大;②基于專用DSP芯片的設計應用范圍受限;③基于通用DSP芯片設計的優點是設計簡便、靈活,特別適合于新型產品的研究開發。

3.1圖像技術對DSP芯片的要求

對于圖像技術來說,由于要處理的數據量大,計算復雜,計算中間結果精度要求高,因此需要選擇合適的DSP芯片。在選擇DSP芯片時首先要考慮對芯片速度的要求。由于現代高性能DSP芯片的結構多樣化,單純依靠指令執行速度MIPS 比較其性能是不全面的,現在一般采用單周期的乘加次數,或采用數字信號處理中的基準程序如FFT和數字濾波等的執行時間來測評DSP芯片的速度性能。其次,還需要考慮如何選擇定點或浮點DSP芯片。

一般說來,浮點DSP芯片的運算精度高,動態范圍大,尋址空間大,指令運算能力較強,但功耗、成本、體積較大。而定點DSP芯片的運算精度與浮點DSP芯片相同(定點的數據位數和浮點的位數相同的情況下),且功耗、成本、體積較小,但動態范圍小,需要防止計算溢出,尋址空間小,指令運算能力較弱。從總體性能上看,浮點DSP芯片優于定點DSP芯片。此外,在硬件方面還應考慮芯片的外部總線結構、片上存儲器結構、DMA功能、串行通信口和芯片間通信能力等因素;在軟件方面主要是開發軟件的功能性、開發時間要求等因素。

綜合考慮DSP芯片的性能和開發設計的要求后,在圖像技術中應該首選浮點DSP芯片,但是在對價格敏感的產品設計中,目前采用定點DSP芯片的例子也有。

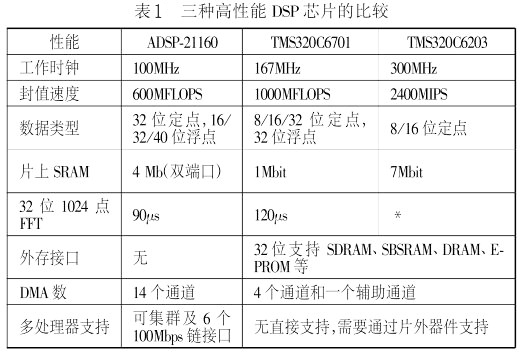

表1比較了代表目前很高DSP芯片技術水平的三種產品,包括TI公司的定點 DSP芯片(TMS320C6203)和浮點DSP芯片(TMS320C6701)與AD公司浮點DSP芯片(ADSP-21160)。由于工作時鐘較高的原因,TI公司的DSP芯片在單芯片處理能力上優于AD公司的產品,但是在多芯片集成處理上AD公司的DSP芯片性能更好一些。

3.2基于DSP芯片的圖像處理系統

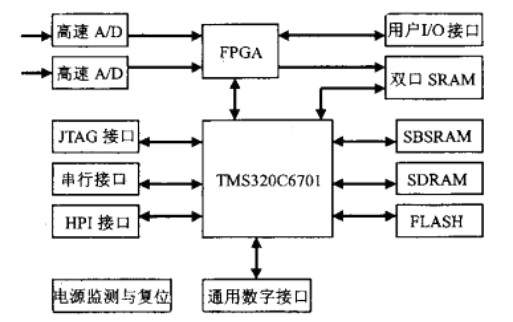

圖2所示為一個獨立型通用圖像處理系統。系統板主要構成為:工作于167MHz的TMS320C6701 ; 32位4M的SDRAM ,32位128K 的SBSRAM,32位4K的雙口RAM,16位1M的Flash存儲器;兩路A/D,每路40M/12Bit,可同時采樣,采樣頻率可變;可編程FPGA作為靈活的接口;通用數字接口也可以直接接收彩色數字圖像;外部HPI主機接口可用于系統控制;仿真調試JTAG接口;串行通信接口;電源監測與復位控制電路等。

在該系統開發板上處理應用于會議電視的CIF格式的彩色圖像,實驗效果較好。TI公司提供了全圖形的Code Composer集成開發環境,具有匯編語言和直接的C編譯器。匯編語言的程序代碼執行效率高,而采用C語言的程序代碼效率較差。但是,直接采用匯編語言編程有一定難度。因此,通常先采用c語言設計驗證算法,然后經過C編譯器產生匯編代碼。最后在匯編代碼的基礎上進行優化。

圖2 獨立型通用圖像處理系統框圖

結束語

以上就是DSP芯片在圖像技術中的應用介紹了。DSP芯片將應用在更多的領域,如智能通信基站、雷達、聲納、圖形圖像系統、語音識別、VOIP、飛行仿真、軍用設備等等。

〈烜芯微/XXW〉專業制造二極管,三極管,MOS管,橋堆等,20年,工廠直銷省20%,上萬家電路電器生產企業選用,專業的工程師幫您穩定好每一批產品,如果您有遇到什么需要幫助解決的,可以直接聯系下方的聯系號碼或加QQ/微信,由我們的銷售經理給您精準的報價以及產品介紹

聯系號碼:18923864027(同微信)

QQ:709211280