電阻在電路中起限制電流的作用,而上拉電阻和下拉電阻是經(jīng)常提到也是經(jīng)常用到的電阻。在每個(gè)系統(tǒng)的設(shè)計(jì)中都用到了大量的上拉電阻和下拉電阻,這兩者統(tǒng)稱為“拉電阻”,最基本的作用是:將狀態(tài)不確定的信號(hào)線通過(guò)一個(gè)電阻將其箝位至高電平(上拉)或低電平(下拉),但是無(wú)論具體用法如何,這個(gè)基本的作用都是相同的,只是在不同應(yīng)用場(chǎng)合中會(huì)對(duì)電阻的阻值要求有所不同,下面一起來(lái)了解它們吧:

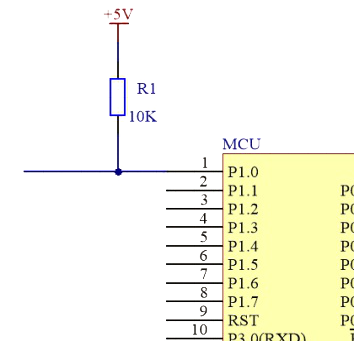

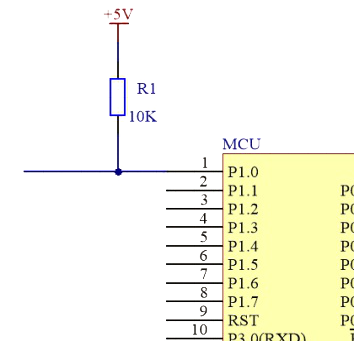

1.上拉電阻

(1)概念:將一個(gè)不確定的信號(hào),通過(guò)一個(gè)電阻與電源VCC相連,固定在高電平。

圖1 上拉電阻

(2)原理:在上拉電阻所連接的導(dǎo)線上,如果外部組件未啟用,上拉電阻則“微弱地”將輸入電壓信號(hào)“拉高”。當(dāng)外部組件未連接時(shí),對(duì)輸入端來(lái)說(shuō),外部“看上去”就是高阻抗的。這時(shí),通過(guò)上拉電阻可以將輸入端口處的電壓拉高到高電平。如果外部組件啟用,它將取消上拉電阻所設(shè)置的高電平。通過(guò)這樣,上拉電阻可以使引腳即使在未連接外部組件的時(shí)候也能保持確定的邏輯電平。

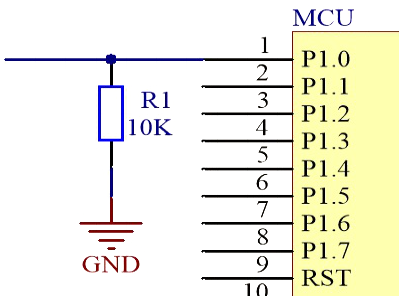

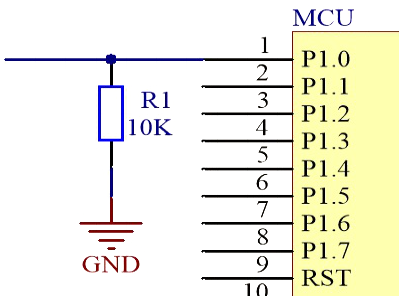

2.下拉電阻

概念:將一個(gè)不確定的信號(hào),通過(guò)一個(gè)電阻與GND相連,固定在低電平。

圖2 下拉電阻

3.主要作用

下拉電阻的主要作用是與上接電阻一起在電路驅(qū)動(dòng)器關(guān)閉時(shí)給線路(節(jié)點(diǎn))以一個(gè)固定的電平。

(1)提高電壓準(zhǔn)位:

a)當(dāng)TTL電路驅(qū)動(dòng)COMS電路時(shí),如果TTL電路輸出的高電平低于COMS電路的最低高電平(一般為3.5V), 這時(shí)就需要在TTL的輸出端接上拉電阻,以提高輸出高電平的值。

b)OC門(mén)電路必須加上拉電阻,以提高輸出的高電平值。

(2)加大輸出引腳的驅(qū)動(dòng)能力,有的單片機(jī)管腳上也常使用上拉電阻。

(3)電阻匹配,抑制反射波干擾:長(zhǎng)線傳輸中電阻不匹配容易引起反射波干擾,加上下拉電阻是電阻匹配,有效的抑制反射波干擾。

(4)N/Apin防靜電、防干擾:在COMS芯片上,為了防止靜電造成損壞,不用的管腳不能懸空,一般接上拉電阻產(chǎn)生降低輸入阻抗,提供泄荷通路。同時(shí)管腳懸空就比較容易接受外界的電磁干擾。

(5)預(yù)設(shè)空間狀態(tài)/缺省電位:在一些CMOS輸入端接上或下拉電阻是為了預(yù)設(shè)缺省電位。當(dāng)你不用這些引腳的時(shí)候,這些輸入端下拉接0或上拉接1。在I2C總線等總線上,空閑時(shí)的狀態(tài)是由上下拉電阻獲得

(6)提高芯片輸入信號(hào)的噪聲容限:輸入端如果是高阻狀態(tài),或者高阻抗輸入端處于懸空狀態(tài),此時(shí)需要加上拉或下拉,以免收到隨機(jī)電平而影響電路工作。同樣如果輸出端處于被動(dòng)狀態(tài),需要加上拉或下拉,如輸出端僅僅是一個(gè)三極管的集電極。從而提高芯片輸入信號(hào)的噪聲容限增強(qiáng)抗干擾能力。

以上就是上拉電阻與下拉電阻的作用介紹了。對(duì)于上拉電阻和下拉電阻的選擇,應(yīng)結(jié)合開(kāi)關(guān)管特性和下級(jí)電路的輸入特性進(jìn)行設(shè)定;考慮的因素包括:驅(qū)動(dòng)能力與功耗的平衡,下級(jí)電路的驅(qū)動(dòng)需求,高低電平的設(shè)定,頻率特性等等。

〈烜芯微/XXW〉專業(yè)制造二極管,三極管,MOS管,橋堆等,20年,工廠直銷省20%,上萬(wàn)家電路電器生產(chǎn)企業(yè)選用,專業(yè)的工程師幫您穩(wěn)定好每一批產(chǎn)品,如果您有遇到什么需要幫助解決的,可以直接聯(lián)系下方的聯(lián)系號(hào)碼或加QQ/微信,由我們的銷售經(jīng)理給您精準(zhǔn)的報(bào)價(jià)以及產(chǎn)品介紹

聯(lián)系號(hào)碼:18923864027(同微信)

QQ:709211280