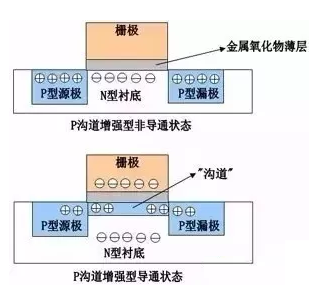

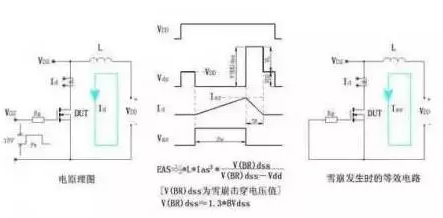

MOS管學名是場效應管,是金屬-氧化物-半導體型場效應管,屬于絕緣柵型。

其結構示意圖:

MOS管失效的6個原因:

1)雪崩失效(電壓失效),也就是我們常說的漏源間的BVdss電壓超過MOSFET的額定電壓,并且超過達到了一定的能力從而導致MOSFET失效。

2)SOA失效(電流失效),既超出MOSFET安全工作區引起失效,分為Id超出器件規格失效以及Id過大,損耗過高器件長時間熱積累而導致的失效。

3)體二極管失效:在橋式、LLC等有用到體二極管進行續流的拓撲結構中,由于體二極管遭受破壞而導致的失效。

4)諧振失效:在并聯使用的過程中,柵極及電路寄生參數導致震蕩引起的失效。

5)靜電失效:在秋冬季節,由于人體及設備靜電而導致的器件失效。

6)柵極電壓失效:由于柵極遭受異常電壓尖峰,而導致柵極柵氧層失效。

具體分析如下:

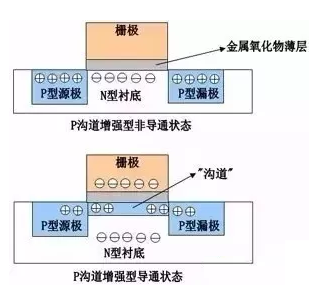

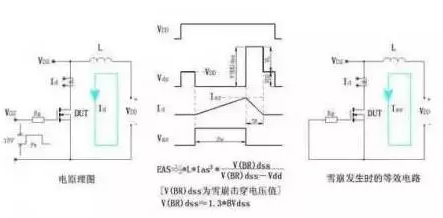

1)雪崩失效分析(電壓失效)

到底什么是雪崩失效呢,簡單來說MOSFET在電源板上由于母線電壓、變壓器反射電壓、漏感尖峰電壓等等系統電壓疊加在MOSFET漏源之間,導致的一種失效模式。簡而言之就是由于就是MOSFET漏源極的電壓超過其規定電壓值并達到一定的能量限度而導致的一種常見的失效模式。

下面的圖片為雪崩測試的等效原理圖,做為電源工程師可以簡單了解下。

可能我們經常要求器件生產廠家對我們電源板上的MOSFET進行失效分析,大多數廠家都僅僅給一個EAS.EOS之類的結論,那么到底我們怎么區分是否是雪崩失效呢,下面是一張經過雪崩測試失效的器件圖,我們可以進行對比從而確定是否是雪崩失效。

雪崩失效的預防措施

雪崩失效歸根結底是電壓失效,因此預防我們著重從電壓來考慮。具體可以參考以下的方式來處理。

1:合理降額使用,目前行業內的降額一般選取80%-95%的降額,具體情況根據企業的保修條款及電路關注點進行選取。

2:合理的變壓器反射電壓。

3:合理的RCD及TVS吸收電路設計。

4:大電流布線盡量采用粗、短的布局結構,盡量減少布線寄生電感。

5:選擇合理的柵極電阻Rg。

6:在大功率電源中,可以根據需要適當的加入RC減震或齊納二極管進行吸收。

2)SOA失效(電流失效)

再簡單說下第二點,SOA失效

SOA失效是指電源在運行時異常的大電流和電壓同時疊加在MOSFET上面,造成瞬時局部發熱而導致的破壞模式。或者是芯片與散熱器及封裝不能及時達到熱平衡導致熱積累,持續的發熱使溫度超過氧化層限制而導致的熱擊穿模式。

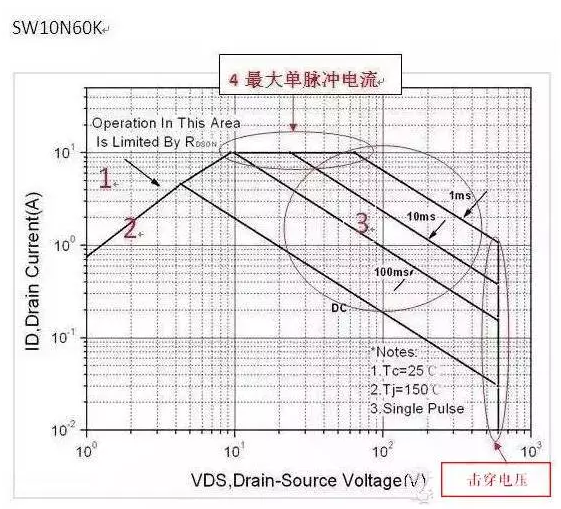

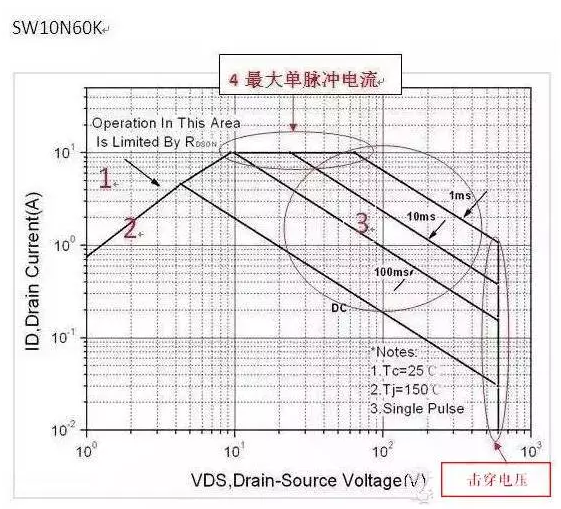

關于SOA各個線的參數限定值可以參考下面圖片。

1:受限于最大額定電流及脈沖電流

2:受限于最大節溫下的RDSON。

3:受限于器件最大的耗散功率。

4:受限于最大單個脈沖電流。

5:擊穿電壓BVDSS限制區

我們電源上的MOSFET,只要保證能器件處于上面限制區的范圍內,就能有效的規避由于MOSFET而導致的電源失效問題的產生。

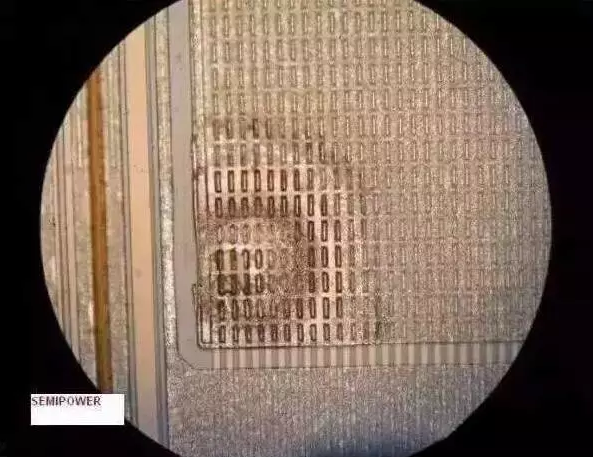

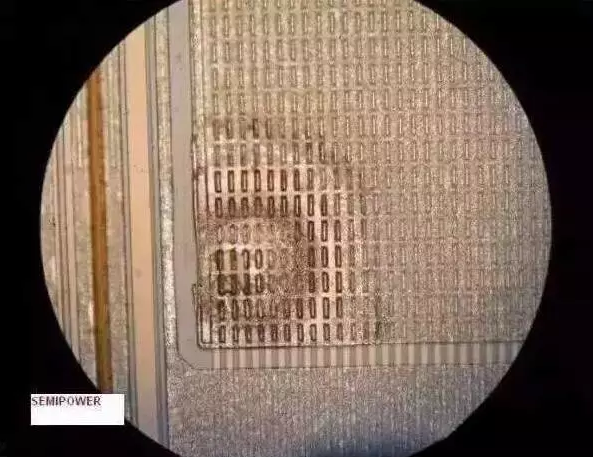

這個是一個非典型的SOA導致失效的一個解刨圖,由于去過鋁,可能看起來不那么直接,參考下。

SOA失效的預防措施

1:確保在最差條件下,MOSFET的所有功率限制條件均在SOA限制線以內。

2:將OCP功能一定要做精確細致。

在進行OCP點設計時,一般可能會取1.1-1.5倍電流余量的工程師居多,然后就根據IC的保護電壓比如0.7V開始調試RSENSE電阻。

有些有經驗的人會將檢測延遲時間、CISS對OCP實際的影響考慮在內。

但是此時有個更值得關注的參數,那就是MOSFET的Td(off)。

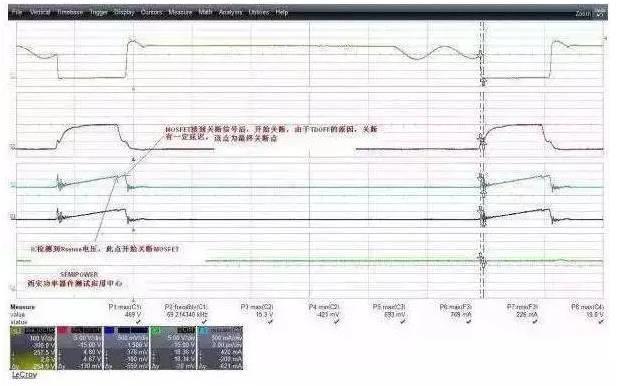

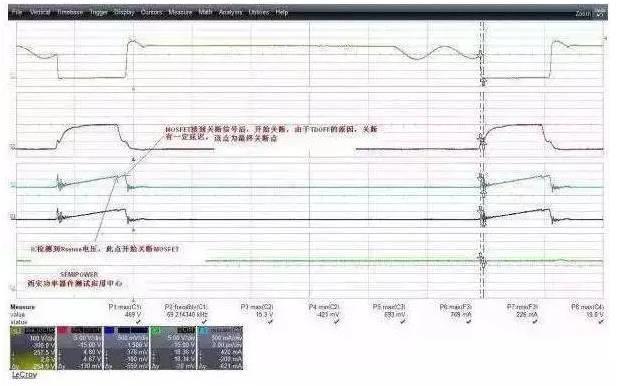

它到底有什么影響呢,我們看下面FLYBACK電流波形圖

從圖中可以看出,電流波形在快到電流尖峰時,有個下跌,這個下跌點后又有一段的上升時間,這段時間其本質就是IC在檢測到過流信號執行關斷后,MOSFET本身也開始執行關斷,但是由于器件本身的關斷延遲,因此電流會有個二次上升平臺,如果二次上升平臺過大,那么在變壓器余量設計不足時,就極有可能產生磁飽和的一個電流沖擊或者電流超器件規格的一個失效。

3:合理的熱設計余量,這個就不多說了,各個企業都有自己的降額規范,嚴格執行就可以了,不行就加散熱器。

3)體二極管失效

在不同的拓撲、電路中,MOSFET有不同的角色,比如在LLC中,體內二極管的速度也是MOSFET可靠性的重要因素。漏源間的體二極管失效和漏源電壓失效很難區分,因為二極管本身屬于寄生參數。雖然失效后難以區分軀體緣由,但是預防電壓及二極管失效的解決辦法存在較大差異,主要結合自己電路來分析。

體二極管失效預防措施

其實有那個體二極管,在大部分時候都不礙事,而且有時候還有好處,比如用在H橋上,省得并二極管了。當然也有礙事的時候,那就用兩個MOS管頭頂頭或者尾對尾串聯起來就可以了。

那個二極管是工藝決定的,也不必太在意,接受它的存在就好了。還有,多說兩句,其實MOS管的D和S本質上是對稱的結構,只是溝道的兩個接點。但是由于溝道的開啟和關閉涉及到柵極和襯底之間的電場,那么就需要給襯底一個確定的電位。又因為MOS管只有3個管腳,所以需要把襯底接到另外兩個管腳之一。那么接了襯底的管腳就是S了,沒接襯底的管腳就是D,我們應用時,S的電位往往是穩定的。在集成電路中,比如CMOS中或者還有模擬開關中,由于芯片本身有電源管腳,所以那些MOS管的襯底并不和管腳接在一起,而是直接接到電源的VCC或者VEE,這時候D和S就沒有任何區別了。

4)諧振失效

在并聯功率MOS FET時未插入柵極電阻而直接連接時發生的柵極寄生振蕩。高速反復接通、斷開漏極-源極電壓時,在由柵極-漏極電容Cgd(Crss)和柵極引腳電感Lg形成的諧振電路上發生此寄生振蕩。當諧振條件(ωL=1/ωC)成立時,在柵極-源極間外加遠遠大于驅動電壓Vgs(in)的振動電壓,由于超出柵極-源極間額定電壓導致柵極破壞,或者接通、斷開漏極-源極間電壓時的振動電壓通過柵極-漏極電容Cgd和Vgs波形重疊導致正向反饋,因此可能會由于誤動作引起振蕩破壞。

諧振失效預防措施

電阻可以抑制振蕩, 是因為阻尼的作用。但柵極串接一個小電阻, 并非解決振蕩阻尼問題. 主要還是驅動電路阻抗匹配的原因, 和調節功率管開關時間的原因。

5)靜電失效

靜電的基本物理特征為:有吸引或排斥的力量;有電場存在,與大地有電位差;會產生放電電流。這三種情形會對電子元件造成以下影響:

1.元件吸附灰塵,改變線路間的阻抗,影響元件的功能和壽命。

2.因電場或電流破壞元件絕緣層和導體,使元件不能工作(完全破壞)。

3.因瞬間的電場軟擊穿或電流產生過熱,使元件受傷,雖然仍能工作,但是壽命受損。

靜電失效的預防措施

MOS電路輸入端的保護二極管,其導通時電流容限一般為1mA 在可能出現過大瞬態輸入電流(超過10mA)時,應串接輸入保護電阻。而129#在初期設計時沒有加入保護電阻,所以這也是MOS管可能擊穿的原因,而通過更換一個內部有保護電阻的MOS管應可防止此種失效的發生。還有由于保護電路吸收的瞬間能量有限,太大的瞬間信號和過高的靜電電壓將使保護電路失去作用。所以焊接時電烙鐵必須可靠接地,以防漏電擊穿器件輸入端,一般使用時,可斷電后利用電烙鐵的余熱進行焊接,并先焊其接地管腳。

6)柵極電壓失效

柵極的異常高壓來源主要有以下3種原因:

1:在生產、運輸、裝配過程中的靜電。

2:由器件及電路寄生參數在電源系統工作時產生的高壓諧振。

3:在高壓沖擊時,高電壓通過Ggd傳輸到柵極(在雷擊測試時,這種原因導致的失效較為常見)。

至于PCB污染等級、電氣間隙及其它高壓擊穿IC后進入柵極等現象就不做過多解釋。

柵極電壓失效的預防措施

柵源間的過電壓保護:如果柵源間的阻抗過高,則漏源間電壓的突變會通過極間電容耦合到柵極而產生相當高的UGS電壓過沖,這一電壓會引起柵極氧化層永久性損壞,如果是正方向的UGS瞬態電壓還會導致器件的誤導通。為此要適當降低柵極驅動電路的阻抗,在柵源之間并接阻尼電阻或并接穩壓值約20V的穩壓管。特別要注意防止柵極開路工作。其次是漏極間的過電壓防護。如果電路中有電感性負載,則當器件關斷時,漏極電流的突變(di/dt)會產生比電源電壓高的多的漏極電壓過沖,導致器件損壞。應采取穩壓管箝位,RC箝位或RC抑制電路等保護措施。

補充下,MOSFET損壞主要有使用/品質工藝兩方面原因

使用方面:

1)靜電損壞,初期可能還象好管子一樣開關,經過一段時間后會失效炸機,GDS全短路.

2)空間等離子損傷,輕者和靜電損壞一樣,重者直接GDS短路.大家要注意啊!放MOSFET或IGBT/COMS器件的地方千萬別用負離子發生器或有此功能的空調!

3)漏電損傷,多數情況下GDS全短路,個別會DS或GD斷路.

4)過驅動,驅動電壓超過18V后,經過一段時間使用會GDS全短.

5)使用負壓關閉,柵加負壓后,MOSFET抗噪能力加強,但DS耐壓能力下降,不適當的負壓,會導致DS耐壓不夠而被擊穿損壞而GDS短路.

6)柵寄生感應負壓損壞,和不適當的負壓驅動一樣,只是該負壓不是人為加上的,是由于線路寄生LC感應,在刪上感應生成負脈沖.

〈烜芯微/XXW〉專業制造二極管,三極管,MOS管,橋堆等,20年,工廠直銷省20%,上萬家電路電器生產企業選用,專業的工程師幫您穩定好每一批產品,如果您有遇到什么需要幫助解決的,可以直接聯系下方的聯系號碼或加QQ/微信,由我們的銷售經理給您精準的報價以及產品介紹

聯系號碼:18923864027(同微信)

QQ:709211280