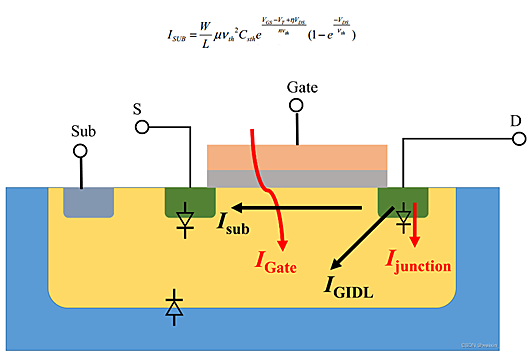

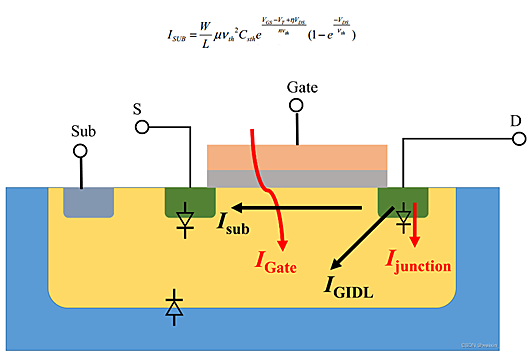

理想的MOS晶體管不應該有任何電流流入襯底或者阱中,當晶體管關閉的時候D\S之間不應該存在任何的電流。但是,現實中MOS卻存在各種不同的漏電流。漏電流一方面嚴重減小了低功耗設備的電池使用壽命,另一方面在某些s&h電路中,極大的限制了信號保持時間。

反偏結泄漏電流,junction leakage(/junction):

結漏泄漏電流為:當晶體管關斷時,通過反偏二極管從源極或漏極到襯底或者阱到襯底;這種反偏結泄露電流主要由兩部分組成:

(1)由耗盡區邊緣的擴散和漂移電流產生;

(2)由耗盡區中的產生的電子-空穴對形成;

對于重摻雜的PN區,還會有帶間隧穿(BTBT)現象貢獻的泄漏電流。源漏二極管和阱二極管的結反向偏置泄漏電流分量相對于其他三個泄漏分量通常可以忽略不計。

柵致漏極泄露電流,gate induced drain leakage (GIDL,/GIDL)

柵致漏極泄露電流是由MOS晶體管漏極結中的高場效應引起的。由于G與D重疊區域之間存在大電場而發生隧穿并產生電子-空穴對,其中包含雪崩隧穿和BTBT隧穿。由于電子被掃入阱中,空穴積累在漏中形成/GIDL。

柵漏重疊區域下的強電場導致了深度耗盡區以及是的漏極和阱交界處耗盡層變薄,因而有效形成漏極到阱的電流/GIDL。/GIDL與VDG有關。/GIDL在NMOS中比在PMOS中還要大兩個數量級。

柵極直接隧穿電流,gate direct tunneling leakage(/G)

柵極泄露電流是有柵極上的電荷隧穿過柵氧化層進入阱(襯底)中形成。一般柵氧化層厚度為3-4 nm,由于在氧化物層上施加高電場,電子通過Fowler-Nordheim隧道進入氧化物層的導帶而產生的/G。

隨著晶體管長度和電源電壓的減小,柵極氧化物的厚度也必須減小以維持對溝道區域的有效柵極控制。不幸的是,由于電子的直接隧穿會導致柵極泄漏呈指數級增加。

目前,有種方法能在克服柵極漏電流的同時保持對柵極進行良好的控制,就是采用諸如TiO2和Ta2O5的高K介電材料替代SiO2做柵極絕緣體介質層。

亞閾值泄露電流,Subthreshold (weak inversion) leakage (/SUB)

亞閾值泄漏電流是指溝道處于弱反型狀態下的源漏電流,是由器件溝道中少數載流子的擴散電流引起的。當柵源電壓低于Vth時,器件不是馬上關閉的,晶體管事實上是進入了“亞閾值區”,在這種情況下,IDS成了VGS的指數函數。

在目前的CMOS技術中,亞閾值泄漏電流ISUB比其他泄漏電流分量大得多。這主要是因為現代CMOS器件中的VT相對較低。ISUB通過使用以下公式計算:

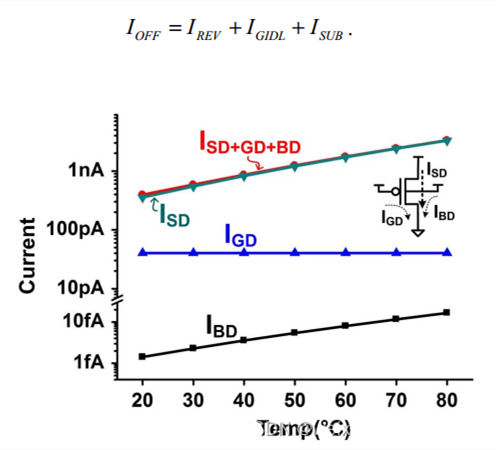

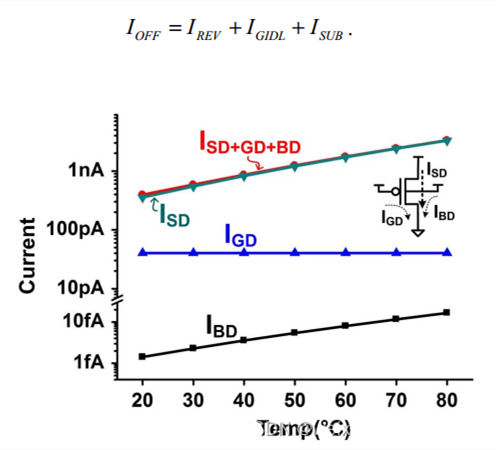

所以MOS管的靜態功耗電流IOFF主要來源:

其中占主要部分的是/SUB。

隧穿柵極氧化層漏電流

在短溝道器件中,薄柵極氧化物會在 SiO 2層上產生高電場。具有高電場的低氧化物厚度導致電子從襯底隧穿到柵極以及從柵極通過柵極氧化物隧穿到襯底,從而導致柵極氧化物隧穿電流。

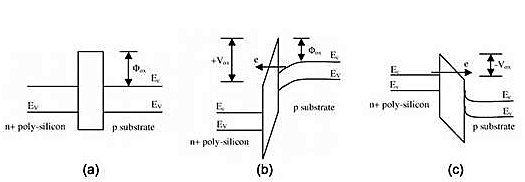

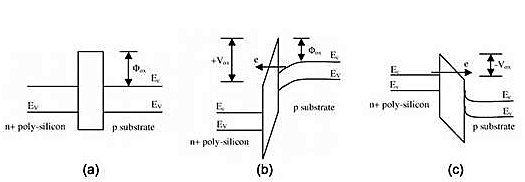

考慮如圖所示的能帶圖。

圖. 具有(a)平帶、(b)正柵極電壓和(c)負柵極電壓的 MOS 晶體管的能帶圖

圖 2(a),是一個平帶 MOS 晶體管,即其中不存在電荷。

當柵極端子正偏置時,能帶圖會發生變化,如圖所示,圖 2(b)。強烈反轉表面處的電子隧道進入或穿過 SiO 2層,從而產生柵極電流。

另一方面,當施加負柵極電壓時,來自 n+ 多晶硅柵極的電子隧道進入或穿過 SiO 2層,從而產生柵極電流,如圖 2(c) 所示。

〈烜芯微/XXW〉專業制造二極管,三極管,MOS管,橋堆等,20年,工廠直銷省20%,上萬家電路電器生產企業選用,專業的工程師幫您穩定好每一批產品,如果您有遇到什么需要幫助解決的,可以直接聯系下方的聯系號碼或加QQ/微信,由我們的銷售經理給您精準的報價以及產品介紹

聯系號碼:18923864027(同微信)

QQ:709211280