功耗

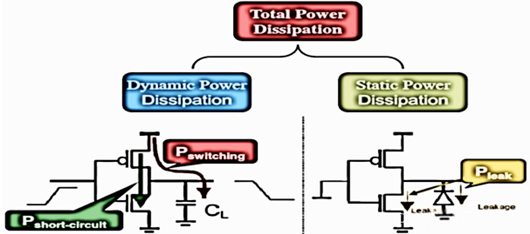

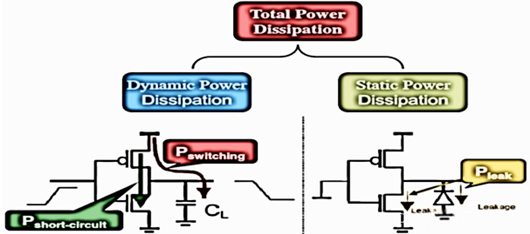

功耗 = 靜態功耗 + 動態功耗

= 靜態功耗 + 轉換功耗 + 短路功耗

功耗源

功耗的本質是能量耗散。由能量守恒定律可知,能量只能從一種形式轉成另一種形式,能量的總量不變。芯片耗散的電能主要轉化成熱能。如果一顆芯片的功耗過大,容易導致工作時溫度過高,造成功能失效,甚至晶體管失效。因此,減小芯片功耗是很重要的一個任務。靜態功耗以及動態功耗是兩個主要的功耗源。

動態功耗

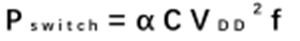

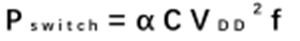

P_dynamic=k*C*V*V*f+m*V*I_sc,和電壓、負載電容、工作時鐘頻率、信號翻轉率、短路電流有關;

電壓角度:

(1)降低工作電壓;

(2)多電壓域;

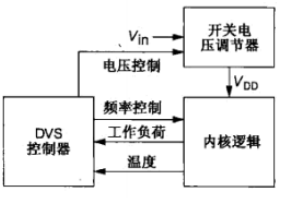

(3)動態電壓縮放DVS技術(處理器在不同工作模式下使用不同電壓);

(4)電源關斷技術,power-gating;

負載電容角度:與工藝有關

(1)按比例縮小集成度,降低器件電容;

(2)多芯片系統中,可以考慮多芯片封裝,減低接口間電容;

(3)合理的布局布線;

工作時鐘頻率角度:

(1)降低工作頻率;

(2)多時鐘域;

(3)門控時鐘,clockgating;

數據翻轉率角度:

(1)使用格雷碼等狀態翻轉比較少的編碼;

(2)數據不操作說,保持上次的值,而不是強制置0或者置1;

(3)使用使能信號、片選信號,減少不必要的切換;

1.動態功耗

動態功耗來源于:

(1)當門翻轉時,負載電容充電和放電,稱為翻轉功耗

(2)pmos和nmos管的串并聯結構都導通時的有短路電流,稱為短路功耗。

1.1翻轉功耗翻轉功耗可以用如下公式表示:

α稱為活動因子,是電路節點從0跳變至1的概率。時鐘的活動因子為1,因為它在每個周期都有上升和下降。大多數數據的活動因子為0.5,每周期只跳變一次。

C稱為負載電容。

有以下辦法可以降低翻轉功耗:

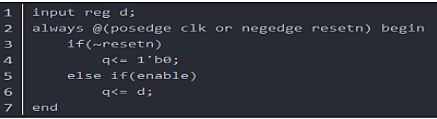

(1)使用門控時鐘降低活動因子是降低功耗的非常有效的辦法,如果一個電路的時鐘完全關斷,那么它的活動因子和動態功耗將降為0。Verilog在設計寄存器時采用下面寫法可以綜合成一個帶門控的寄存器。

(2)減小毛刺毛刺會增大活動因子,有可能使門的活動因子增加到1以上。

(3)減小負載電容電容來自于電路中的連線以及晶體管。縮短連線長度,良好的平面規劃和布局可以使連線電容減小。選擇較小的邏輯級數以及較小的晶體管可以減小器件的翻轉電容。

(4)電壓域動態功耗與電壓有平方的關系,降低電源電壓可以顯著降低功耗。將芯片劃分成多個電壓域,每個電壓域可以根據特定電路的需要進行優化。例如,對于存儲器采用高電源電壓來保證存儲單元的穩定性,對于處理器采用中等大小的電壓,對運行速度較低的IO外圍電路采用低電壓。解決跨電壓域信號傳輸的方法是使用電平轉換器。

(5)動態電壓調整DVSCPU處理不同的任務有不同的性能要求。對于低性能要求的任務,可以使時鐘頻率降低到足以按預定時間完成任務的最低值,然后使電壓降低到該頻率下工作所需要的最小值就可以節省大量的能耗。

(6)降低頻率動態功耗正比于頻率,芯片只應當工作在所要求的頻率下,不能比所要求的還要快。由前面小結可以,降低頻率還可以采用較低的電源電壓,大大降低功耗。

(7)諧振電路諧振電路通過使能量在儲能元件如電容或電感之間來回傳送而不是將能量泄放到來減小翻轉功耗。

1.2短路功耗

短路功耗發生在當輸入發生翻轉時,上拉和下拉網絡同時部分導通的時候。如果輸入信號翻轉速率比較慢,那這兩個網絡將同時導通較長的一段時間,短路功耗也會比較大,增大負載電容可以減小短路功耗,原因是負載較大時,輸出在輸入跳變期間只翻轉變化很小的一個量。

短路電流一般為負載電流的10%。當輸入邊沿變化速度很快時,短路功耗一般只占翻轉功耗的2%-10%。

〈烜芯微/XXW〉專業制造二極管,三極管,MOS管,橋堆等,20年,工廠直銷省20%,上萬家電路電器生產企業選用,專業的工程師幫您穩定好每一批產品,如果您有遇到什么需要幫助解決的,可以直接聯系下方的聯系號碼或加QQ/微信,由我們的銷售經理給您精準的報價以及產品介紹

〈烜芯微/XXW〉專業制造二極管,三極管,MOS管,橋堆等,20年,工廠直銷省20%,上萬家電路電器生產企業選用,專業的工程師幫您穩定好每一批產品,如果您有遇到什么需要幫助解決的,可以直接聯系下方的聯系號碼或加QQ/微信,由我們的銷售經理給您精準的報價以及產品介紹

聯系號碼:18923864027(同微信)

QQ:709211280