MOS管根據(jù)導(dǎo)電性質(zhì)不同可分為NMOS和PMOS兩種。NMOS和PMOS的結(jié)構(gòu)相似,都是由n型和p型半導(dǎo)體夾雜著一層氧化膜構(gòu)成的。不同之處在于,NMOS的氧化膜上覆蓋著一層金屬,通常是鎢或銅,而PMOS則覆蓋著一層氮化硅或氧化鋁等絕緣材料。

NMOS和PMOS的特性區(qū)別

NMOS的導(dǎo)通電阻小,通常用于低電壓、大電流的場合,例如電源開關(guān)和放大器等;而PMOS的阻斷電壓高,通常用于高電壓、小電流的場合,例如場效應(yīng)晶體管和電源控制器等。

如何快速區(qū)分nmos和pmos

1.通過外觀區(qū)分

NMOS和PMOS的外觀有時可以通過肉眼觀察來區(qū)分。通常情況下,NMOS的管芯顏色較深,呈灰色或黑色,而PMOS的管芯顏色較淺,呈淡黃色或淡藍色。

2.通過標識區(qū)分

NMOS和PMOS的標識也可以用來區(qū)分它們。通常情況下,NMOS的標識為“N”,而PMOS的標識為“P”。

3.通過電路特性區(qū)分

在實際應(yīng)用中,可以通過電路特性來區(qū)分NMOS和PMOS。通常情況下,NMOS的導(dǎo)通電阻小,可以在低電壓、大電流的場合使用;而PMOS的阻斷電壓高,可以在高電壓、小電流的場合使用。

nmos和pmos區(qū)別

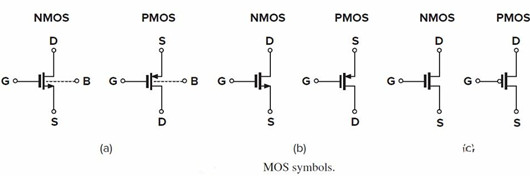

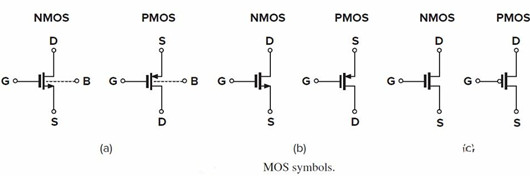

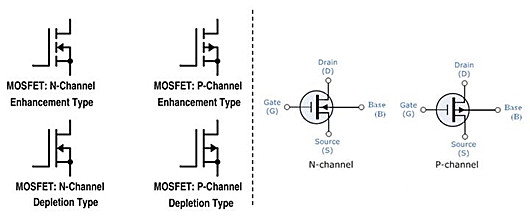

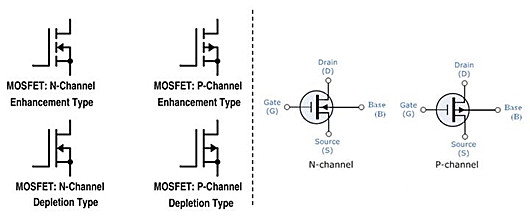

PMOS和NMOS的源漏方位相反,NMOS的漏端drain在上面,PMOS的源端source在上面,之所以這么做是借助方位來表明電位的高低。NMOS的漏端drain和PMOS的源端source的電壓都比柵端gate電壓高,所以這么標注獲得一個“visualaid”。電流方向是一致的,如果采用箭頭表示電流方向,都是從上到下的。

如果是四端口畫法,箭頭的方向就不是電流方向,而是襯底和溝道之間的PN結(jié)方向,和二極管一樣,都是從P端指到N端。

NMOS是N型溝道,P型襯底,襯底接最低電位,PMOS是P型溝道,N型襯底接最高電位。這樣是為了源漏端和襯底形成P-N結(jié)反偏,不然電流從源漏端直接正向?qū)ǖ降亍舸┱f的也是這個P-N結(jié)反向擊穿。因為溝道和襯底的材料不同,所以柵壓變化才會有耗盡層-反型層形成的說法。

NMOS的溝道材料是N型,而襯底材料是P型,所以柵極需要加正電壓,才能排斥P型襯底里的空穴,吸引電子聚集在溝道的下方,和柵極的金屬板構(gòu)成柵電容。電容的介質(zhì)材料是SiO2。PMOS的溝道材料是P型,而襯底材料是N型,要想在N型材料里吸引空穴的話,自然柵極應(yīng)該加負電壓。和NMOS柵極正電壓越大,溝道的導(dǎo)電能力越強一樣,PMOS是柵極電壓負向越大,溝道導(dǎo)電能力越強。

nmos pmos工作條件不同

溝道形成條件

現(xiàn)在來看一下工作條件,NMOS,VGS>VthV_{GS}>V_{th}和VDS>VGS?VthV_{DS}>V_{GS}-V_{th},前者是用來保證導(dǎo)電溝道的形成,疊加后者的條件就是飽和狀態(tài)。導(dǎo)通條件到PMOS這,是以柵端電壓對比襯底電壓VDDV_{DD}較小為好,這樣空穴就會被吸附到表面形成溝道,所以可以看出閾值電壓VthV_{th}為負值。這和NMOS的VthV_{th}的正值恰相反,注意這里不涉及增強型還是耗盡型管子的區(qū)分。考慮襯底和源端相連,導(dǎo)通條件是VGS<VthV_{GS}<V_{th},如果用絕對值表示|VGS|>|Vth||V_{GS}|>|V_{th}|。電流的流動從方位上和NMOS沒有區(qū)別,都是從上方流到下方。

飽和條件

飽和區(qū)的條件類比較為麻煩,因為飽和區(qū)形成的微觀機理稍微復(fù)雜一點。首先我們要弄清,為什么對于NMOS,當VDS>VGS?VthV_{DS}>V_{GS}-V_{th}就有IDI_D飽和呢?當滿足了VGS>VthV_{GS}>V_{th},溝道里從漏端到源端的電壓都是一樣的,可以等效為簡單的平行板電容器。但是MOS管是個立體結(jié)構(gòu),除了平行板的垂直電場,要形成電流還需要水平方向的電場,也就是從漏極到源級的電場。水平方向的電場NMOS是漏端最高,源端最低,沿著溝道方向電勢逐漸降低。

溝道處的電勢由固定的襯底電勢疊加水平方向的電勢,就造成了柵平行板電容雖然柵極電壓不變,但襯底邊的電壓不均勻。對于NMOS來說,需要保證VGS>VthV_{GS}>V_{th},這里S換成sub(襯底)會更好理解,VG?Sub>VthV_{G-Sub}>V_{th},但現(xiàn)在襯底電壓因為施加了VDSV_{DS}不再保持均勻相等。靠近漏端這一端的電壓VGDV_{GD}要比VGSV_{GS}小,因為漏端電壓高。隨著漏端電壓的提升,VGDV_{GD}會率先小于VthV_{th},這樣漏端這個地方就形成了夾斷(pinch-off),但這個夾斷和VG?Sub<VthV_{G-Sub}<V_{th}時的截止不一樣,稱為預(yù)夾斷,是通過VDSV_{DS}破壞了VG?Sub>VthV_{G-Sub}>V_{th}的條件形成的夾斷,且只有漏端一點夾斷了,不是整個溝道都夾斷了。但是,溝道的預(yù)夾斷正是我們需要的,因為夾斷后漏端和柵端就連接起來的了。

這里其實是有點問題的,因為按照前面的器件模型,夾斷后VGDV_{GD}是等于VthV_{th}的,繼續(xù)增大VDV_D可以繼續(xù)減小VGDV_{GD},造成小于VthV_{th}的情況。但這里的假設(shè)是,VGDV_{GD}減小到VthV_{th}的時候,柵端和漏端連接起來,這樣無論VDV_D如何變化,夾斷點都等于VthV_{th},整個溝道的水平電壓也就保持不變了。這里不考慮channel-lengthmodulation的情況。夾斷以后,器件模型就類似是diode-connected的電路拓撲了,柵端和漏端連接,器件始終工作在飽和區(qū)。不過不同的是,器件里降低VDV_D可以回到線性區(qū),而在電路里,降低VDV_D回不到線性區(qū),只能直接進入截止區(qū)。

根據(jù)前面的分析,可以知道NMOS進入飽和區(qū)的要求是VGD<VthV_{GD}<V_{th},換成常用的是VDS>VGS?VthV_{DS}>V_{GS}-V_{th}。PMOS因為柵端電壓負與襯底端,所以施加VSDV_{SD}后,漏端的電壓最低,且低的柵端電壓高于漏端電壓不超過閾值電壓了,破壞了柵電壓構(gòu)筑的導(dǎo)通條件,所以有VGD>VthV_{GD}>V_{th},換算一下,VDS<VGS?VthV_{DS}<V_{GS}-V_{th}。

總結(jié)

對于NMOS,柵端gate比襯底端substrate高一個VthV_{th},才能形成溝道,要破壞這個溝道,柵端gate比漏端drain高,但不能高于VthV_{th},才能形成預(yù)夾斷,工作在飽和區(qū)。

VGS>Vth,VGD<VthV_{GS}>V_{th},V_{GD}<V_{th},后一個條件即VDS>VGS?VthV_{DS}>V_{GS}-V_{th}

對于PMOS,柵端gate比襯底端substrate低過負閾值電壓VthV_{th},才可以吸附空穴,形成反型層,柵端gate比漏端drain低,但不能低過VthV_{th},形成溝道破壞條件,才能工作在飽和區(qū)。

VGS<Vth,VGD>VthV_{GS}<V_{th},V_{GD}>V_{th},后一個條件即VDS<VGS?VthV_{DS}<V_{GS}-V_{th},考慮VthV_{th}是負值,也可以改為|VGS|>|Vth|,|VDS|>|VGS|?|Vth||V_{GS}|>|V_{th}|,|V_{DS}|>|V_{GS}|-|V_{th}|,這樣和NMOS的條件就有了一定的統(tǒng)一性。

NMOS和PMOS的應(yīng)用領(lǐng)域

NMOS的應(yīng)用領(lǐng)域

NMOS廣泛應(yīng)用于數(shù)字電路、開關(guān)電源、計算機內(nèi)存等領(lǐng)域。在數(shù)字電路中,NMOS常用于設(shè)計與門、或門、非門等邏輯門電路;在開關(guān)電源中,NMOS常用于設(shè)計開關(guān)管和調(diào)整管等;在計算機內(nèi)存中,NMOS常用于設(shè)計DRAM和SRAM等存儲器。

PMO的應(yīng)用領(lǐng)域

PMOS主要用于高頻電路、射頻電路、傳感器等領(lǐng)域。在高頻電路中,PMOS常用于設(shè)計高頻開關(guān)和調(diào)制器等;在射頻電路中,PMOS常用于設(shè)計射頻開關(guān)和衰減器等;在傳感器領(lǐng)域,PMOS常用于設(shè)計壓力傳感器、溫度傳感器等。

〈烜芯微/XXW〉專業(yè)制造二極管,三極管,MOS管,橋堆等,20年,工廠直銷省20%,上萬家電路電器生產(chǎn)企業(yè)選用,專業(yè)的工程師幫您穩(wěn)定好每一批產(chǎn)品,如果您有遇到什么需要幫助解決的,可以直接聯(lián)系下方的聯(lián)系號碼或加QQ/微信,由我們的銷售經(jīng)理給您精準的報價以及產(chǎn)品介紹

聯(lián)系號碼:18923864027(同微信)

QQ:709211280