超結功率MOSFET輸出電容遲滯效應產生原因

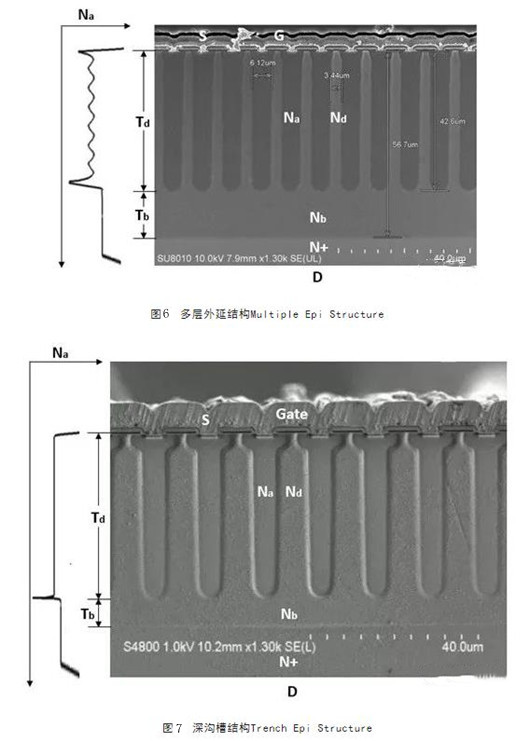

超結功率MOSFET技術目前采取多層外延和深溝槽工藝,相對于平面結構,P阱下移形成P柱結構,如圖6、圖7所示。通常情況,超結功率MOSFET的COSS在充電過程中,超結N柱、P柱最初的移動載流子,會在放電過程中完全消耗盡。

但是,如果在COSS充電階段,一些移動載流子被隔離滯留,也就是形成滯留電荷(Stranded Charges QSTR),耗盡層擴展不一致,沿著N柱、P柱形成沒有耗盡的微小區域,導致充電和放電過程不一致,最終形成遲滯效應,也就是COSS充放電過程中一些能量在內部被消耗。超結功率MOSFET輸出電容遲滯效應,和滯留電荷直接相關。

從圖5可以發現,超結功率MOSFET輸出電容的遲滯效應,與其漏極源極所加電壓VDS直接相關,這種效應大多發生在低壓階段,這也表明,超結功率MOSFET輸出電容的遲滯效應和超結柱狀結構在低于100V發生的三維耗盡有關。

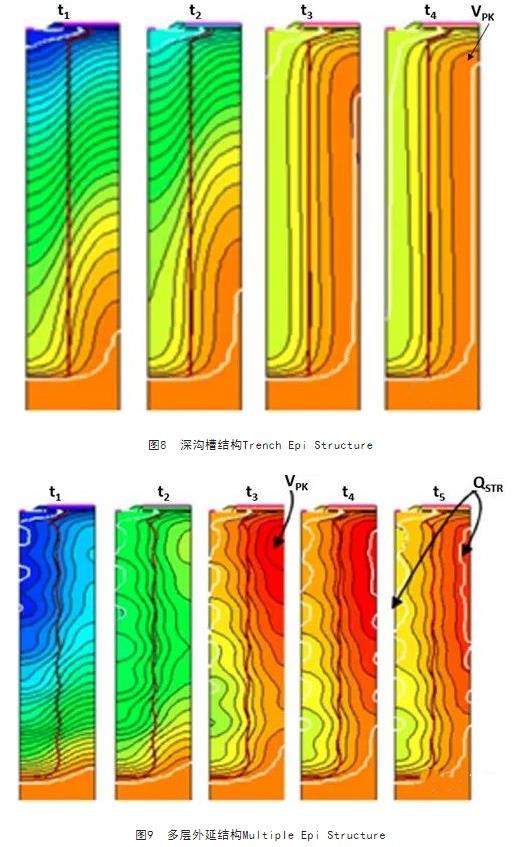

此外,COSS的遲滯效應也和超結功率MOSFET結構相關,內部晶胞單元尺寸越小,遲滯效應越明顯。相關文獻研究表明:深溝槽結構沒有滯留電荷QSTR效應,多層外延結構具有滯留電荷QSTR效應,如圖8、圖9所示。

圖8和圖9中,列出了這種結構的仿真電勢線分布圖Potential line distribution。多層外延結構在動態耗盡過程中,滯留電荷QSTR,出現在N柱和P柱的底部和頂部。

Jaume Roig and Filip Bauwens, Origin of Anomalous COSS Hysteresis in Resonant Converters With Superjunction FETs

這表明:多層外延結構MEMI(Multi implant multi epitaxy)的滯留電荷QSTR效應,比深溝槽結構TFET(Trench filling epitaxial growth)要嚴重。

超結功率MOSFET輸出電容遲滯效應的功耗測量

為了得到超結功率MOSFET輸出電容遲滯效應所產生的功耗,可以用等效法測量。

超結功率MOSFET輸出電容遲滯回線的測量電路和陶瓷電容的測量電路類似,根據電路,在一定輸入電壓、工作頻率fs下穩定工作,測量超結功率MOSFET殼頂的溫升ΔT。

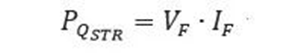

然后,在超結功率MOSFET內部寄生二極管通過一定電流IF,使超結功率MOSFET殼頂的溫升同樣達到ΔT,測量寄生二極管壓降VF,則可以得到相應條件下,

輸出電容遲滯效應所產生的功耗:

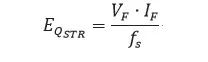

輸出電容遲滯效應所產生的能量:

〈烜芯微/XXW〉專業制造二極管,三極管,MOS管,橋堆等,20年,工廠直銷省20%,上萬家電路電器生產企業選用,專業的工程師幫您穩定好每一批產品,如果您有遇到什么需要幫助解決的,可以直接聯系下方的聯系號碼或加QQ/微信,由我們的銷售經理給您精準的報價以及產品介紹

聯系號碼:18923864027(同微信)

QQ:709211280