在I2C主從設(shè)備對(duì)接時(shí),需要考慮主從設(shè)備的電平情況,常規(guī)的主要有3種:5V,3.3V,1.8V。如果電平相同,比如都是3.3V,那么可以直接對(duì)接。如果電平不同,一個(gè)高電平是3.3V ,另外一個(gè)是1.8V,那么就需要接入其它的器件來(lái)做一下電平轉(zhuǎn)換,通常是接入NMOS管。

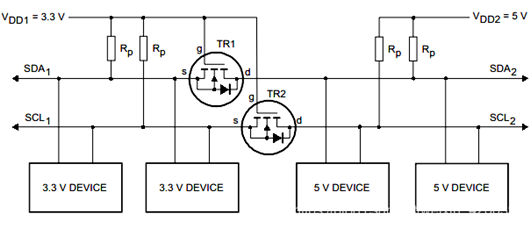

通過(guò)使用雙向電平轉(zhuǎn)換器可以將電源電壓和邏輯電平不同的兩部分I2C 總線連接起來(lái)配置入下圖所示。左邊的低電壓部分有上拉電阻而且器件連接到3.3V 的電源電壓,右邊的高電平部分有上拉電阻器件連接到5V 電源電壓。兩部分的器件都有與邏輯輸入電平相關(guān)的電源電壓和開(kāi)漏輸出配置的I/O。

每條總線線路的電平轉(zhuǎn)換器是相同的而且由一個(gè)分立的N通道增強(qiáng)型MOS-FET管串行數(shù)據(jù)線SDA的TR1和串行時(shí)鐘線SCL 的TR2 組成。門(mén)極g 要連接到電源電壓VDD1, 源極s 連接到低電壓部分的總線線路而漏極d 則連接到高電壓部分的總線線路。

很多MOS-FET 管的基底與它的源極內(nèi)部連接,如果內(nèi)部沒(méi)有,就必須建立一個(gè)外部連接。因此,每個(gè)MOS-FET 管在漏極和基底之間都有一個(gè)集成的二極管n-p 結(jié)。如下圖所示。

電平轉(zhuǎn)換器的操作

在電平轉(zhuǎn)換器的操作中要考慮下面的三種狀態(tài):

1、 沒(méi)有器件下拉總線線路。

低電壓部分的總線線路通過(guò)上拉電阻Rp 上拉至VDD1(3.3V) MOS-FET 管的門(mén)極和源極都是VDD1(3.3V), 所以它的VGS 低于閥值電壓MOS-FET 管不導(dǎo)通這就允許高電壓部分的總線線路通過(guò)它的上拉電阻Rp 拉到5V。 此時(shí)兩部分的總線線路都是高電平只是電壓電平不同。

2、一個(gè)3.3V 器件下拉總線線路到低電平。

MOS-FET 管的源極也變成低電平而門(mén)極是VDD1(3.3V)。VGS高于閥值,MOS-FET 管開(kāi)始導(dǎo)通然后高電壓部分的總線線路通過(guò)導(dǎo)通的MOS-FET管被VDD1(3.3V)器件下拉到低電平,此時(shí)兩部分的總線線路都是低電平而且電壓電平相同。

3、一個(gè)5V 的器件下拉總線線路到低電平。

MOS-FET 管的漏極基底、二極管低電壓部分被下拉,直到VGS 超過(guò)閥值,MOS-FET 管開(kāi)始導(dǎo)通,低電壓部分的總線線路通過(guò)導(dǎo)通的MOS-FET管被5V 的器件進(jìn)一步下拉到低電平,此時(shí)兩部分的總線線路都是低電平而且電壓電平相同。

這三種狀態(tài)顯示了邏輯電平在總線系統(tǒng)的兩個(gè)方向上傳輸,與驅(qū)動(dòng)的部分無(wú)關(guān)。狀態(tài)1 執(zhí)行了電平轉(zhuǎn)換功能,狀態(tài)2和3按照I2C總線規(guī)范的要求在兩部分的總線線路之間實(shí)現(xiàn)“線與”的功能。除了VDD1 (3.3V)和VDD2 (5.0V)的電源電壓外,還可以是例如2V VDD1 和10V VDD2 等的正常操作。其中VDD2必須等于或高于VDD1 。

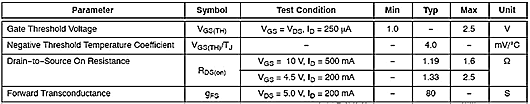

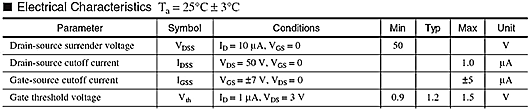

但是值得注意的是,VDD1作為較低部分的電壓,必須能夠大于所選擇的MOS-FET的閥值電壓,也就是必須能夠打開(kāi)MOS-FET。此管參數(shù)必須謹(jǐn)慎選擇。如下兩種參數(shù)MOS-FET,在VDD1 (1.8V)到VDD2 (3.0V) 的電路中就可能存在截然不同的效果。

管1

管2

選擇管1,由于VGS的范圍是1.0~2.5V,很有可能出現(xiàn)大于1.8V的狀況,因此VDD1方面?zhèn)鬏數(shù)碗娖叫盘?hào)時(shí),MOS-FET不能很完全的被打開(kāi),導(dǎo)致到VDD2 (3.0V)方面的信號(hào)不能徹底為低,出現(xiàn)半高狀態(tài)。

選擇管2,由于VGS的范圍是0.9~1.5V小于1.8V,因此,通路才會(huì)正常工作。

其他不同電壓間的轉(zhuǎn)換原理如上,請(qǐng)悉心選擇器件。

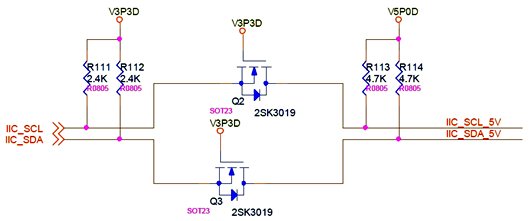

在3.3V IIC總線中用到5V IIC器件,該電路已實(shí)驗(yàn)通過(guò)。

〈烜芯微/XXW〉專業(yè)制造二極管,三極管,MOS管,橋堆等,20年,工廠直銷省20%,上萬(wàn)家電路電器生產(chǎn)企業(yè)選用,專業(yè)的工程師幫您穩(wěn)定好每一批產(chǎn)品,如果您有遇到什么需要幫助解決的,可以直接聯(lián)系下方的聯(lián)系號(hào)碼或加QQ/微信,由我們的銷售經(jīng)理給您精準(zhǔn)的報(bào)價(jià)以及產(chǎn)品介紹

聯(lián)系號(hào)碼:18923864027(同微信)

QQ:709211280