抗干擾能力對于MOS管驅動電路是一個重要指標,MOS管不是工作在一個理想的沒有任何電磁干擾的環境,在一些電磁環境惡劣的條件下,如果我們的驅動電路設計的不盡合理,可能會出現MOS管誤打開或者非受控關斷,輕則影響性能,重則會對用戶造成傷害。

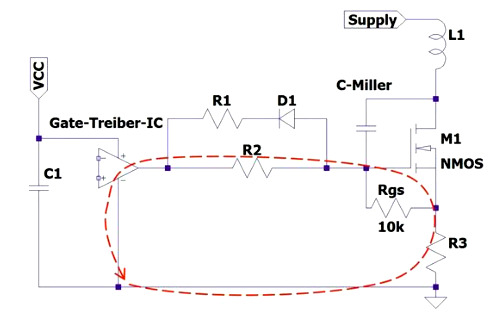

對于MOS管驅動電路而言,這種情況的發生一般是由于gate-source寄生米勒電容的非正常充放電導致的,而影響因素主要是gate極等效串聯電阻,寄生電感,寄生電容等因素,所以我們主要針對這三方面進行針對性電路設計來提升電路的抗干擾能力。

提升抗干擾的針對措施

1.柵極串聯電阻降低源極寄生電感導致的振蕩

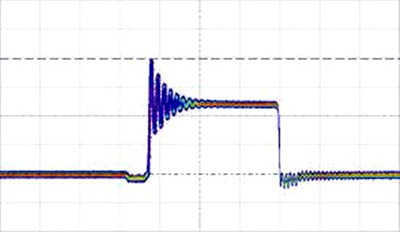

我們在實際調試MOS管驅動電路時,如果大家用示波器測一下MOS管gate極的波形,就會發現MOS管每次打開時,其柵極波形會出現類似于正弦波的阻尼振蕩,這不僅使得MOS開關不穩定,降低其抗干擾能力,也會增大開關損耗,那么為什么會出現?如何解決呢?

MOS開/關振蕩

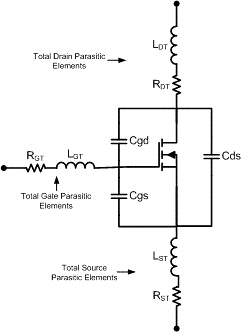

實際的MOS模型大家可以參考下圖,理想的MOS沒有Rgt,Lgt,以及Cgs等,但是現實的MOS這些都有,此時你會發現,Rgt+Lgt+Cgs那不就成了典型的RLC振蕩電路么,沒錯就是這樣;

所以當我們給高電平想開啟MOS的時候,就會出現振鈴波,同樣我們給低電平想關閉MOS時也是一樣,都是電容電感的充放電在作妖。

理解了原因,那么如何解決這一問題呢?

解決問題的關鍵就是Rgt電阻,因為對于RLC振蕩電路而言,Rgt是耗能器件,每一次振蕩,它都會消耗能量,從而減弱下一次的振蕩幅值,這也是實際的波形峰值越來越低的原因;

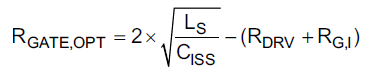

當然Rgt是MOS內部的寄生電阻,其阻值很小,所以我們一般需要外部在串聯一個電阻,串聯電阻的阻值計算公式如下,其中Rdv是外部PCB網絡走線寄生電阻,電阻大了能緩解電壓過沖的問題,但是也不是越大越好,因為太大了又會導致MOS開啟速度過慢,所以需要綜合考慮。

2.柵源并聯電阻提升抗dv/dt干擾能力

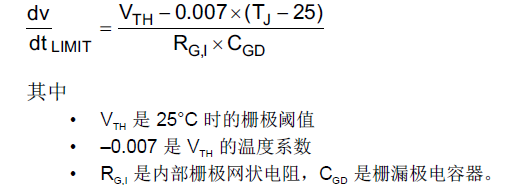

當dv/dt過大時,可以會使得MOS誤打開,這是由于流過Cgd電容的電流在G極形成正壓,從而引起MOS誤打開,通常通過在器件的柵極和源極端子間加入一個電阻器來提供保護,電阻的計算公式參考下面;

根據公式可以看出來,要想計算我們需要多大的并聯電阻,還需要清楚我們的電路最差的dv/dt是多少,這個就需要實際測試了。

本文主要講解了提升MOS管驅動電路抗干擾能力的方法以及計算方式。

〈烜芯微/XXW〉專業制造二極管,三極管,MOS管,橋堆等,20年,工廠直銷省20%,上萬家電路電器生產企業選用,專業的工程師幫您穩定好每一批產品,如果您有遇到什么需要幫助解決的,可以直接聯系下方的聯系號碼或加QQ/微信,由我們的銷售經理給您精準的報價以及產品介紹

聯系號碼:18923864027(同微信)

QQ:709211280