隨著數(shù)字電路的普及,傳統(tǒng)的定制數(shù)字集成電路器件已滿足不了應(yīng)用的需求,因此可編程邏輯器件(PLD)應(yīng)運(yùn)而生,并逐漸成為主流產(chǎn)品。PLD與傳統(tǒng)定制器件的主要區(qū)別是它的可編程性,它的邏輯功能是由用戶設(shè)計(jì)的,并且一般都可重復(fù)編程和擦除。下面一起來(lái)了解可編程邏輯器件的相關(guān)知識(shí)。

1.基本概念

可編程邏輯器件 英文全稱為:programmable logic device 即 PLD。PLD是做為一種通用集成電路產(chǎn)生的,他的邏輯功能按照用戶對(duì)器件編程來(lái)確定。一般的PLD的集成度很高,足以滿足設(shè)計(jì)一般的數(shù)字系統(tǒng)的需要。這樣就可以由設(shè)計(jì)人員自行編程而把一個(gè)數(shù)字系統(tǒng)“集成”在一片PLD上,而不必去請(qǐng)芯片制造廠商設(shè)計(jì)和制作專用的集成電路芯片了。

PLD與一般數(shù)字芯片不同的是:PLD內(nèi)部的數(shù)字電路可以在出廠后才規(guī)劃決定,有些類型的PLD也允許在規(guī)劃決定后再次進(jìn)行變更、改變,而一般數(shù)字芯片在出廠前就已經(jīng)決定其內(nèi)部電路,無(wú)法在出廠后再次改變,事實(shí)上一般的模擬芯片、混訊芯片也都一樣,都是在出廠后就無(wú)法再對(duì)其內(nèi)部電路進(jìn)行調(diào)修。

典型的PLD一般都是二級(jí)結(jié)構(gòu),通常第一級(jí)為“與陣列”,第二級(jí)為“或陣列”。由“與陣列”輸入,進(jìn)行邏輯“與”組合,形成乘積項(xiàng),再由這些不同的乘積項(xiàng)通過(guò)“或陣列”構(gòu)成所需求的邏輯函數(shù)輸出。

可編程邏輯器件

2.優(yōu)點(diǎn)

(1)PLD允許客戶在需要時(shí)僅訂購(gòu)所需要的數(shù)量,從而使客戶可控制庫(kù)存。

(2)PLD不需要漫長(zhǎng)的前置時(shí)間來(lái)制造原型或正式產(chǎn)品,PLD器件已經(jīng)放在分銷商的貨架上并可隨時(shí)付運(yùn)。

(3)PLD甚至在設(shè)備付運(yùn)到客戶那兒以后還可以重新編程。客戶可根據(jù)需要修改電路直到對(duì)設(shè)計(jì)工作感到滿意為止。一旦設(shè)計(jì)完成,客戶可立即投入生產(chǎn),只需要利用最終軟件設(shè)計(jì)文件簡(jiǎn)單地編程所需要數(shù)量的PLD就可以了。

(4)PLD不需要客戶支付高昂的NRE成本和購(gòu)買昂貴的掩模組,設(shè)計(jì)人員可利用價(jià)格低廉的軟件工具快速開發(fā)、仿真和測(cè)試其設(shè)計(jì)。然后,可快速將設(shè)計(jì)編程到器件中,并立即在實(shí)際運(yùn)行的電路中對(duì)設(shè)計(jì)進(jìn)行測(cè)試。原型中使用的PLD器件與正式生產(chǎn)最終設(shè)備(如網(wǎng)絡(luò)路由器、DSL調(diào)制解調(diào)器、DVD播放器、或汽車導(dǎo)航系統(tǒng))時(shí)所使用的PLD完全相同。

復(fù)雜可編程邏輯器件

3.分類

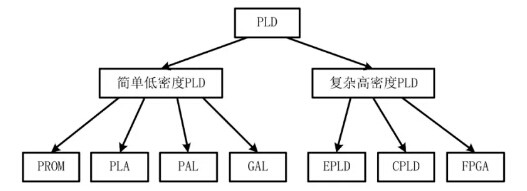

根據(jù)PLD器件的“與陣列”和“或陣列”的編程情況及輸出形式,可編程邏輯器件通常可分為如下四類:

第一類:“與陣列”固定、“或陣列”可編程的PLD器件

以可編程只讀存儲(chǔ)器(PROM)為代表??删幊讨蛔x存儲(chǔ)器(PROM)是組合邏輯陣列,它包含一個(gè)固定的“與陣列”和一個(gè)可編程的“或陣列”,其中的“與陣列”是全譯碼形式,它產(chǎn)生輸入變量的所有最小項(xiàng)。

PROM的每個(gè)輸出端通過(guò)“與陣列”將這些最小項(xiàng)有選擇地進(jìn)行“或”運(yùn)算,即可實(shí)現(xiàn)任何組合邏輯函數(shù)。由于“與陣列”能夠產(chǎn)生輸入變量的全部最小項(xiàng),所以用PROM實(shí)現(xiàn)組合邏輯函數(shù)不需要進(jìn)行邏輯化簡(jiǎn)。但隨著輸入變量數(shù)的增加,“與陣列”的規(guī)模會(huì)迅速增大,其價(jià)格也隨之大大提高,而且“與陣列”越大,譯碼開關(guān)時(shí)間就越長(zhǎng),相應(yīng)的工作速度也越慢。因此,實(shí)際上只有規(guī)模較小的PROM可以有效的實(shí)現(xiàn)組合邏輯函數(shù),而大規(guī)模的PROM價(jià)格高、工作速度低,一般只作為存儲(chǔ)器使用。

第二類:“與陣列”和“或陣列”均可編程的PLD器件

以可編程邏輯陣列(PLA)器件為代表。PLA的“與陣列”不是全譯碼形式,它可以通過(guò)編程控制只產(chǎn)生函數(shù)最簡(jiǎn)與或式中所需要的“與”項(xiàng)。因此,PLA器件的“與陣列”規(guī)模減小,集成度相對(duì)提高。

由于PLA只產(chǎn)生函數(shù)最簡(jiǎn)與或式中所需要的“與”項(xiàng),因此PLA在編程前必須先進(jìn)行函數(shù)化簡(jiǎn)。另外,PLA器件需要對(duì)兩個(gè)陣列進(jìn)行編程,編程難度較大,而且PLA器件的開發(fā)工具應(yīng)用不廣泛,編程一般由生產(chǎn)廠家完成。

第三類:“與陣列”可編程、“或陣列”固定的PLD器件

以可編程陣列邏輯(PAL)器件為代表。這類器件的每個(gè)輸出時(shí)若干個(gè)乘積項(xiàng)之或,其中乘積項(xiàng)的數(shù)目固定。通常PPAL的乘積項(xiàng)數(shù)允許達(dá)到8個(gè),而一般邏輯函數(shù)的最簡(jiǎn)與或式中僅需要完成3~4個(gè)乘積項(xiàng)“或”運(yùn)算。因此,PLA的這種陣列結(jié)構(gòu)很容易滿足大多數(shù)邏輯函數(shù)的設(shè)計(jì)要求。

PAL有幾種固定的輸出結(jié)構(gòu),如專用輸出結(jié)構(gòu)、可編程I/O結(jié)構(gòu)、帶反饋的寄存器輸出結(jié)構(gòu)及異或型輸出結(jié)構(gòu)等。一種輸出結(jié)構(gòu)只能實(shí)現(xiàn)一定類型的邏輯函數(shù),其通用性較差,這就給PAL器件的管理及應(yīng)用帶來(lái)了不便。

第四類:具有可編程輸出邏輯宏單元的通用PLD器件

以可編程通用陣列邏輯(GAL)器件為主要代表。GAL器件的陣列結(jié)構(gòu)與PAL器件相同,都是采用“與陣列”可編程而“或陣列”固定的形式。兩者的主要區(qū)別是輸出結(jié)構(gòu)不同。PLA器件的輸出結(jié)構(gòu)是固定的,一種結(jié)構(gòu)對(duì)應(yīng)一種類型芯片。如果系統(tǒng)中需要幾種不同的輸出形式,就必須選擇多種芯片來(lái)實(shí)現(xiàn)。GAL器件的每個(gè)輸出端都集成有一個(gè)輸出邏輯宏單元(OLMC)。

輸出邏輯宏單元是可編程的,通過(guò)編程可以決定該電路完成組合邏輯還是時(shí)序邏輯功能,是否需要產(chǎn)生反饋信號(hào),并能實(shí)現(xiàn)輸出使能控制及輸出極性選擇等。因此,GAL器件通過(guò)對(duì)OLMC的編程可以實(shí)現(xiàn)PAL的各種輸出結(jié)構(gòu),使芯片具有很強(qiáng)的通用性和靈活性。如圖所示是可編程邏輯器件的集成密度分類。

可編程邏輯器件的集成密度分類

4.編程語(yǔ)言

可編程邏輯器件的編程語(yǔ)言為hardware description language(硬件描述語(yǔ)言),簡(jiǎn)稱:HDL。HDL并非僅有一種,而是有許多種,如ABEL、AHDL、Confluence、CUPL、HDCal、JHDL、Lava、Lola、MyHDL、PALASM、RHDL等都是,但目前最具知名也最普遍使用的是VHDL與Verilog。

5.PLD開發(fā)工具

基于高復(fù)雜度PLD器件的開發(fā),在很大程度上要依靠電子設(shè)計(jì)自動(dòng)化(EDA)來(lái)完成。PLD的EDA工具以計(jì)算機(jī)軟件為主,將典型的單元電路封裝起來(lái)形成固定模塊并形成標(biāo)準(zhǔn)的硬件開發(fā)語(yǔ)言(如HDL語(yǔ)言)供設(shè)計(jì)人員使用。設(shè)計(jì)人員考慮如何將可組裝的軟件庫(kù)和軟件包搭建出滿足需求的功能模塊甚至完整的系統(tǒng)。PLD開發(fā)軟件需要自動(dòng)地完成邏輯編譯、化簡(jiǎn)、分割、綜合及優(yōu)化、布局布線、仿真以及對(duì)于特定目標(biāo)芯片的適配編譯和編程下載等工作。典型的EDA工具中必須包含兩個(gè)特殊的軟件包,即綜合器和適配器。綜合器的功能就是將設(shè)計(jì)者在EDA平臺(tái)上完成的針對(duì)某個(gè)系統(tǒng)項(xiàng)目的HDL、原理圖或狀態(tài)圖形描述,針對(duì)給定的硬件系統(tǒng)組件,進(jìn)行編譯、優(yōu)化、轉(zhuǎn)換和綜合。

隨著開發(fā)規(guī)模的級(jí)數(shù)性增長(zhǎng),就必須減短PLD開發(fā)軟件的編譯時(shí)間、并提高其編譯性能以及提供豐富的知識(shí)產(chǎn)權(quán)(IP)核資源供設(shè)計(jì)人員調(diào)用。此外,PLD開發(fā)界面的友好性以及操作的復(fù)雜程度也是評(píng)價(jià)其性能的重要因素。

簡(jiǎn)單可編程邏輯器件

本文總結(jié)了可編程邏輯器件的基本概念、分類、編程語(yǔ)言以及開發(fā)工具。總而言之,可編程邏輯器件是一種用戶可以根據(jù)自己的實(shí)際需要使用硬件描述語(yǔ)言編程來(lái)確定邏輯功能的集成電路、芯片。

電話:18923864027(同微信)

QQ:709211280

〈烜芯微/XXW〉專業(yè)制造二極管,三極管,MOS管,橋堆等,20年,工廠直銷省20%,上萬(wàn)家電路電器生產(chǎn)企業(yè)選用,專業(yè)的工程師幫您穩(wěn)定好每一批產(chǎn)品,如果您有遇到什么需要幫助解決的,可以直接聯(lián)系下方的聯(lián)系號(hào)碼或加QQ/微信,由我們的銷售經(jīng)理給您精準(zhǔn)的報(bào)價(jià)以及產(chǎn)品介紹