DDS一般指DDS信號(hào)發(fā)生器,其采用直接數(shù)字頻率合成(Direct Digital Synthesis,簡(jiǎn)稱DDS)技術(shù),與第二代基于鎖相環(huán)頻率合成技術(shù)相比,DDS具有頻率切換時(shí)間短、頻率分辨率高、相位可連續(xù)變化和輸出波形靈活等優(yōu)點(diǎn)。該技術(shù)的常用方法是利用性能優(yōu)良的DDS專用器件,“搭積木”式設(shè)計(jì)電路,這種“搭積木”式設(shè)計(jì)電路方法雖然直觀,但DDS專用器件價(jià)格較貴,輸出波形單一,使用受到一定限制,特別不適合于輸出波形多樣化的應(yīng)用場(chǎng)合。隨著高速可編程邏輯器件FPGA的發(fā)展,電子工程師可根據(jù)實(shí)際需求,在單一FPGA上開(kāi)發(fā)出性能優(yōu)良的具有任意波形的DDS系統(tǒng),極大限度地簡(jiǎn)化設(shè)計(jì)過(guò)程并提高效率。因此本文介紹了利用FPGA設(shè)計(jì)的基于DDS的信號(hào)發(fā)生器。

1.DDS技術(shù)原理

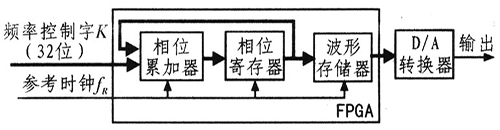

DDS是一種從相位概念出發(fā)直接合成所需波形的數(shù)字頻率合成技術(shù),主要通過(guò)查波形表實(shí)現(xiàn)。由奈奎斯特抽樣定理理論可知,當(dāng)抽樣頻率大于被抽樣信號(hào)的頻率2倍時(shí),通過(guò)抽樣得到的數(shù)字信號(hào)可通過(guò)一個(gè)低通濾波器還原成原來(lái)的信號(hào)。DDS信號(hào)發(fā)生器,主要由相位累加器、相位寄存器、波形存儲(chǔ)器、D/A轉(zhuǎn)換器和模擬低通濾波器組成如圖1所示。fR為參考時(shí)鐘,K為輸入頻率控制字,其值與輸出頻率相對(duì)應(yīng),因此,控制輸入控制字K,就能有效控制輸出頻率值。通常情況下,K值由控制器寫(xiě)入。

圖1 DDS信號(hào)發(fā)生器組成原理

由圖1可知,在參考時(shí)鐘fR的控制下,頻率控制字K與相位寄存器的輸出反饋在相位累加器中完成加運(yùn)算,并把計(jì)算結(jié)果寄存于相位寄存器,作為下加運(yùn)算的一個(gè)輸入值。相位累加器輸出高位數(shù)據(jù)作為波形存儲(chǔ)器的相位抽樣地址值,查找波形存儲(chǔ)器中相對(duì)應(yīng)單元的電壓幅值,得到波形二進(jìn)制編碼,實(shí)現(xiàn)相位到電壓幅值的轉(zhuǎn)變。波形二進(jìn)制編碼再通過(guò)D/A轉(zhuǎn)換器,把數(shù)字信號(hào)轉(zhuǎn)換成相應(yīng)的模擬信號(hào)。低通濾波器可進(jìn)一步濾除模擬信號(hào)中的高頻成分,平滑模擬信號(hào)。在整個(gè)過(guò)程中,當(dāng)相位累加器產(chǎn)生溢出時(shí),DDS系統(tǒng)就完成一個(gè)周期輸出任務(wù)。頻率控制字K與輸出波形頻率的函數(shù)表達(dá)關(guān)系式為:

f0=(K/2N)fR (1)

式中,K為頻率控制字;fR為參考時(shí)鐘,N為累加器的位寬值。

當(dāng)K=l時(shí),可得DDS的分辨率為:

fmin=fR/2 (2)

為了得到較小分辨率,在實(shí)際工程設(shè)計(jì)中,N一般取得較大值,該系統(tǒng)是N取32位設(shè)計(jì)的。

2.器件選擇

本設(shè)計(jì)所用到的關(guān)鍵器件主要是可編程邏輯器件(FPGA)和D/A轉(zhuǎn)換器。考慮設(shè)計(jì)成本等因素,F(xiàn)PGA采用Altera公司的低成本Cyclone系列EPlC6Q240C8。該器件采用邏輯陣列模塊(LAB)和查找表(LUT)結(jié)構(gòu),內(nèi)核采用1.5 V電壓供電,是低功耗元件。此外,Cyclone系列EPlC60240C8內(nèi)部資源豐富,其內(nèi)部?jī)?nèi)嵌5 980個(gè)邏輯單元(LE),20個(gè)4 KB雙口存儲(chǔ)單元(M 4 KB RAM block)和92 160 bit普通高速RAM等資源,因此,能較好滿足該系統(tǒng)設(shè)計(jì)要求。而D/A轉(zhuǎn)換器則采用National Semiconductor公司的DAC0832。

3.DDS的FPGA實(shí)現(xiàn)

3.1相位累加器與相位寄存器的設(shè)計(jì)

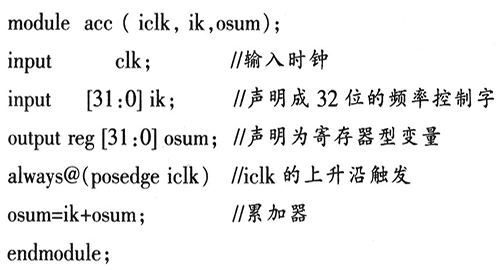

相位累加器與相位寄存器主要完成累加,實(shí)現(xiàn)輸出波形頻率可調(diào)功能。利用Quartus II可編程邏輯器件系統(tǒng)開(kāi)發(fā)工具進(jìn)行設(shè)計(jì)。首先,打開(kāi)Quartus II軟件,新建一個(gè)工程管理文件,然后在此工程管理文件中新建一個(gè)Verilog HDL源程序文件,并用硬件描述語(yǔ)言Verilog HDL編寫(xiě)程序?qū)崿F(xiàn)其功能。在設(shè)計(jì)過(guò)程中,可在一個(gè)模塊中描述。一個(gè)參考的Verilog HDL程序如下:

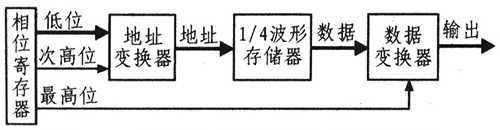

3.2基于1/4波形的存儲(chǔ)器設(shè)計(jì)

為了提高系統(tǒng)的分辨率和降低FPGA資源的利用率,采用基于1/4波形的存儲(chǔ)器設(shè)計(jì)技術(shù)。利用正弦波對(duì)稱性特點(diǎn),只要存儲(chǔ)[O~π/2]幅值,通過(guò)地址和幅值數(shù)據(jù)變換,即可得到整個(gè)周期內(nèi)的正弦波,其設(shè)計(jì)原理如圖2所示。

圖2 波形的存儲(chǔ)器設(shè)計(jì)原理圖

用相位累加器輸出高2位,作為波形區(qū)間標(biāo)志位。當(dāng)位與次高位都為“0”時(shí),表示輸出正弦波正處在[0~π/2]區(qū)間內(nèi),這時(shí),地址與輸出數(shù)據(jù)都不需要變換;當(dāng)位為“0”,次高位為“l”時(shí),輸出正弦波正處在[π/2~π]區(qū)間內(nèi),這時(shí),地址變換器對(duì)地址進(jìn)行求補(bǔ)操作,而輸出數(shù)據(jù)不變;當(dāng)位為“l”,次高位為“0”時(shí),輸出正弦波正處在[π~3π/2]區(qū)間內(nèi),這時(shí),地址不變,而輸出變換器對(duì)輸出數(shù)據(jù)進(jìn)行求補(bǔ)操作;當(dāng)位與次高位都為“l”時(shí),輸出正弦波正處在[3π/2~2π]區(qū)間內(nèi),這時(shí),地址和輸出數(shù)據(jù)都進(jìn)行求補(bǔ)操作。

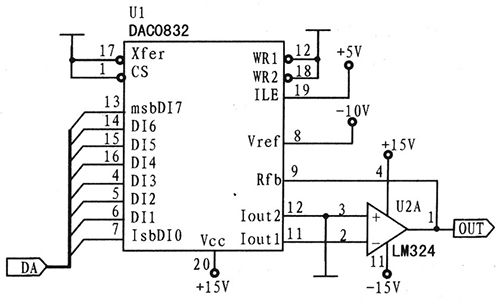

4.D/A轉(zhuǎn)換電路

數(shù)據(jù)轉(zhuǎn)換器輸出的數(shù)據(jù)是數(shù)字形式的電壓值,為實(shí)現(xiàn)數(shù)字電壓值與模擬電壓值之間的轉(zhuǎn)換,系統(tǒng)還專門設(shè)計(jì)D/A轉(zhuǎn)換電路,其D/A轉(zhuǎn)換電路原理圖如圖3所示。

圖3 D/A轉(zhuǎn)換電路

為降低設(shè)計(jì)成本,采用8位廉價(jià)DAC0832作為轉(zhuǎn)換器。該器件是倒T型電阻網(wǎng)絡(luò)型D/A轉(zhuǎn)換器,因其內(nèi)部無(wú)運(yùn)算放大器,輸出為電流,所以要外接運(yùn)算放大器,本文采用LM324型運(yùn)算放大器。DAC0832可根據(jù)實(shí)際情況接成雙緩沖、單緩沖和直沖3種形式,這里采用第3種連接形式,即引腳1、引腳2、引腳17、引腳18接低電平,引腳19接+5 V。引腳8為參考電壓輸入端口.接至+1O V的電源,當(dāng)數(shù)字輸入端全為高電平時(shí),模擬輸出端為+10 V。

5.驗(yàn)證結(jié)果

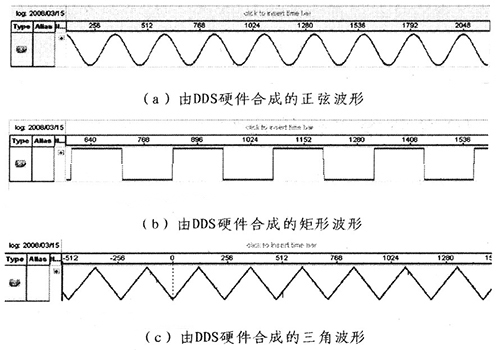

為驗(yàn)證本系統(tǒng)的設(shè)計(jì)正確性,利用Ouarlus II軟件的嵌入式邏輯分析儀分析信號(hào)的波形。在工程管理文件中,首先新建一個(gè)SignalTap文件,并在SignalTap文件中添加要驗(yàn)證的信號(hào)引腳和設(shè)置相關(guān)的參數(shù),然后保存、編譯和到EPlC6Q240C8中,再啟動(dòng)嵌入式邏輯分析儀就可實(shí)時(shí)觀察到相應(yīng)的引腳波形,圖4為在硬件環(huán)境中應(yīng)用嵌入式邏輯分析儀觀察到的波形。其中,圖4a為由DDS硬件合成的正弦波形;圖4b為由DDS硬件合成的矩形波形;圖4c為由DDS硬件合成的三角波形。觀察結(jié)果表明,該系統(tǒng)輸出的各種波形穩(wěn)定,與設(shè)計(jì)要求一致,從而有效驗(yàn)證了該設(shè)計(jì)的正確性。

圖4 DDS信號(hào)波形

總結(jié)

以上就是基于FPGA與DDS的信號(hào)源實(shí)現(xiàn)設(shè)計(jì)介紹了。直接數(shù)字頻率合成(DDS)技術(shù)屬第三代頻率合成技術(shù),與第二代基于鎖相環(huán)頻率合成技術(shù)相比,利用DDS技術(shù)合成的輸出波形具有良好的性能指標(biāo);并從測(cè)試結(jié)果可看出,該系統(tǒng)工作穩(wěn)定、可靠,并具有較好的參考與實(shí)用價(jià)值。

電話:18923864027(同微信)

QQ:709211280

〈烜芯微/XXW〉專業(yè)制造二極管,三極管,MOS管,橋堆等,20年,工廠直銷省20%,上萬(wàn)家電路電器生產(chǎn)企業(yè)選用,專業(yè)的工程師幫您穩(wěn)定好每一批產(chǎn)品,如果您有遇到什么需要幫助解決的,可以直接聯(lián)系下方的聯(lián)系號(hào)碼或加QQ/微信,由我們的銷售經(jīng)理給您精準(zhǔn)的報(bào)價(jià)以及產(chǎn)品介紹