如今,片上系統(tǒng)(SoC)技術(shù)的出現(xiàn)在數(shù)字系統(tǒng)設(shè)計(jì)引起變動(dòng);為適應(yīng)產(chǎn)品盡快上市的要求,設(shè)計(jì)者必須合理選擇各EDA廠家提供的加速設(shè)計(jì)的工具軟件,以使其產(chǎn)品在本領(lǐng)域良性發(fā)展。而FPGA設(shè)計(jì)是當(dāng)前數(shù)字系統(tǒng)設(shè)計(jì)領(lǐng)域中的重要方式之一。本文介紹采用多種EDA工具進(jìn)行FPGA設(shè)計(jì)的實(shí)現(xiàn)原理及方法,并以實(shí)際操作介紹了整個(gè)FPGA的設(shè)計(jì)流程。

1.數(shù)字邏輯劃分與FPGA結(jié)構(gòu)

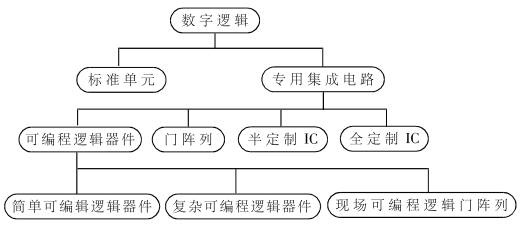

圖1所示為數(shù)字邏輯權(quán)狀分類圖,由其可以看出,現(xiàn)場(chǎng)可編程門(mén)陣列(FPGA)是專用集成電路中可編程邏輯器件的重要分支。隨著微電子工業(yè)的發(fā)展與進(jìn)步,F(xiàn)PGA的集成度已經(jīng)達(dá)到數(shù)百萬(wàn)門(mén),如Xilinx公司的Xcv3200e最大門(mén)數(shù)為320萬(wàn)門(mén),Altera公司的Apex20k1500e為150萬(wàn)門(mén),且系統(tǒng)時(shí)鐘頻率已達(dá)到200MHz,支持多種I/I電壓標(biāo)準(zhǔn),并具有豐富的可重復(fù)利用的IP核,便于加速系統(tǒng)設(shè)計(jì)。

FPGA的內(nèi)部資源(以Xilinx公司為例)一般分為可編程邏輯塊CLB、輸入輸出塊IOB和可編程連線PI三部分。通過(guò)編程控制PI連接各CLB單元,可以形成具有特定功能的電路。使用各公司的專用設(shè)計(jì)軟件設(shè)計(jì)FPGA,最終可形成由PI控制CLB單元的位流文件。

圖1 數(shù)字邏輯樹(shù)狀分類圖

Xilinx公司主推的Virtex系列FPGA產(chǎn)品采用0.22微米工藝,具有如下特性:支持9種I/O標(biāo)準(zhǔn)、4個(gè)延時(shí)鎖定環(huán)、塊存儲(chǔ)與分布存儲(chǔ)并存、可編程流水延時(shí)存儲(chǔ)、熱控制、配置速率為500Mb/s。而Altera公司的Apex20ke系列同樣是其公司主推的FPGA產(chǎn)品,在內(nèi)部嘏線資源方面與Xilinx公司產(chǎn)品不同。在Virtex器件中,分為雙長(zhǎng)線、單長(zhǎng)線、長(zhǎng)線幾種,在布線時(shí)可以按最近原則進(jìn)行取舍;而在Apex20ke中,連線僅為一種等長(zhǎng),所以在時(shí)序分析時(shí)比較準(zhǔn)確。

2.FPGA設(shè)計(jì)流程

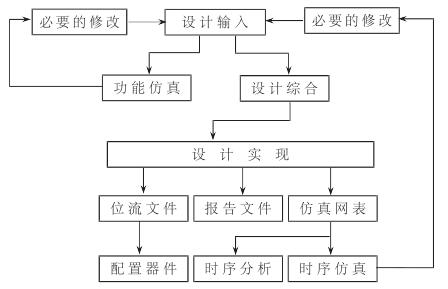

FPGA設(shè)計(jì)人體分為設(shè)計(jì)輸入、綜合、功能仿真(前仿真)、實(shí)現(xiàn)、時(shí)序仿真(后仿真)、配置下載等六個(gè)步驟,設(shè)計(jì)流程如圖2所示。下面分別介紹各個(gè)設(shè)計(jì)步驟。

圖2 FPGA設(shè)計(jì)流程圖

2.1設(shè)計(jì)輸入

設(shè)計(jì)輸入包括使用硬件描述語(yǔ)言HDL、狀態(tài)圖與原理圖輸入三種方式。HDL設(shè)計(jì)方式是現(xiàn)今設(shè)計(jì)大規(guī)模數(shù)字集成電路的良好形式,除IEEE標(biāo)準(zhǔn)中VHDL與Verilog HDL兩種形式外,尚有各自FPGA廠家推出的專用語(yǔ)言,如Quartus下的AHDL。HDL語(yǔ)言描述在狀態(tài)機(jī)、控制邏輯、總線功能方面較強(qiáng),使其描述的電路能特定綜合器(如Synopsys公司的FPGA Compiler II或FPGA Express)作用下以具體硬件單元較好地實(shí)現(xiàn);而原理圖輸入在頂層設(shè)計(jì)、數(shù)據(jù)通路邏輯、手工最優(yōu)化電路等方面具有圖形化強(qiáng)、單元節(jié)儉、功能明確等特點(diǎn),另外,在Altera公司Quartus軟件環(huán)境下,可以使用Momory Editor對(duì)內(nèi)部memory進(jìn)行直接編輯置入數(shù)據(jù)。常用方式是以HDL語(yǔ)言為主,原理圖為輔,進(jìn)行混合設(shè)計(jì)以發(fā)揮二者各自特色。

通常,F(xiàn)PGA廠商軟件與第三方軟件設(shè)有接口,可以把第三方設(shè)計(jì)文件導(dǎo)入進(jìn)行處理。如Quartus與FoundaTIon都可以把EDIF網(wǎng)表作為輸入網(wǎng)表而直接進(jìn)行布局布線,布局布線后,可再將生成的相應(yīng)文件交給第三方進(jìn)行后續(xù)處理。

2.2設(shè)計(jì)綜合

綜合,就是針對(duì)給定的電路實(shí)現(xiàn)功能和實(shí)現(xiàn)此電路的約束條件,如速度、功耗、成本及電路類型等,通過(guò)計(jì)算機(jī)進(jìn)行優(yōu)化處理,獲得一個(gè)能滿足上述要求的電路設(shè)計(jì)方案。也就是是說(shuō),被綜合的文件是HDL文件(或相應(yīng)文件等),綜合的依據(jù)是邏輯設(shè)計(jì)的描述和各種約束條件,綜合的結(jié)果則是一個(gè)硬件電路的實(shí)現(xiàn)方案,該方案必須同時(shí)滿足預(yù)期的功能和約束條件。對(duì)于綜合來(lái)說(shuō),滿足要求的方案可能有多個(gè),綜合器將產(chǎn)生一個(gè)最優(yōu)的或接近最優(yōu)的結(jié)果。因此,綜合的過(guò)程也就是設(shè)計(jì)目標(biāo)的優(yōu)化過(guò)程,最后獲得的結(jié)構(gòu)與綜合器的工作性能有關(guān)。

FPGA Compiler II是一個(gè)完善的FPGA邏輯分析、綜合和優(yōu)化工具,它從HDL形式未優(yōu)化的網(wǎng)表中產(chǎn)生優(yōu)化的網(wǎng)表文件,包括分析、綜合和優(yōu)化三個(gè)步驟。其中,分析是采用Synopsys標(biāo)準(zhǔn)的HDL語(yǔ)法規(guī)則對(duì)HDL源文件進(jìn)行分析并糾正語(yǔ)法錯(cuò)誤;綜合是以選定的FPGA結(jié)構(gòu)和器件為目標(biāo),對(duì)HDL和FPGA網(wǎng)表文件進(jìn)行邏輯綜合;而優(yōu)化則是根據(jù)用戶的設(shè)計(jì)約束對(duì)速度和面積進(jìn)行邏輯優(yōu)化,產(chǎn)生一個(gè)優(yōu)化的FPGA網(wǎng)表文件,以供FPGA布局和布線工具使用,即將電路優(yōu)化于特定廠家器件庫(kù),獨(dú)立于硅持性,但可以被約束條件所驅(qū)動(dòng)。

利用FPGA Compiler II進(jìn)行設(shè)計(jì)綜合時(shí),應(yīng)在當(dāng)前Project下導(dǎo)入設(shè)計(jì)源文件,自動(dòng)進(jìn)行語(yǔ)法分析,在語(yǔ)法無(wú)誤并確定綜合方式、目標(biāo)器件、綜合強(qiáng)度、多層保持選擇、優(yōu)化目標(biāo)等設(shè)置后,即可進(jìn)行綜合與優(yōu)化。在此可以將兩步獨(dú)立進(jìn)行,在兩步之間進(jìn)行約束指定,如時(shí)鐘的確定、通路與端口的延時(shí)、模塊的算子共享、寄存器的扇出等。如果設(shè)計(jì)模型較大,可以采用層次化方式進(jìn)行綜合,先綜合下級(jí)模塊,后綜合上級(jí)模塊。在進(jìn)行上級(jí)模塊綜合埋設(shè)置下級(jí)模塊為Don't Touch,使設(shè)計(jì)與綜合過(guò)程合理化。綜合后形成的網(wǎng)表可以以EDIF格式輸出,也可以以VHDL或Verilog HDL格式輸出,將其導(dǎo)入FPGA設(shè)計(jì)廠商提供的可支持第三方設(shè)計(jì)輸入的專用軟件中,就可進(jìn)行后續(xù)的FPGA芯片的實(shí)現(xiàn)。綜合完成后可以輸出報(bào)告文件,列出綜合狀態(tài)與綜合結(jié)果,如資源使用情況、綜合后層次信息等。

2.3仿真驗(yàn)證

從廣義上講,設(shè)計(jì)驗(yàn)證包括功能與時(shí)序仿真和電路驗(yàn)證。仿真是指使用設(shè)計(jì)軟件包對(duì)已實(shí)現(xiàn)的設(shè)計(jì)進(jìn)行完整測(cè)試,模擬實(shí)際物理環(huán)境下的工作情況。前仿真是指僅對(duì)邏輯功能進(jìn)行測(cè)試模擬,以了解其實(shí)現(xiàn)的功能否滿足原設(shè)計(jì)的要求,仿真過(guò)程沒(méi)有加入時(shí)序信息,不涉及具體器件的硬件特性,如延時(shí)特性;而在布局布線后,提取有關(guān)的器件延遲、連線延時(shí)等時(shí)序參數(shù),并在此基礎(chǔ)上進(jìn)行的仿真稱為后仿真,它是接近真實(shí)器件運(yùn)行的仿真。

2.4 設(shè)計(jì)實(shí)現(xiàn)

實(shí)現(xiàn)可理解為利用實(shí)現(xiàn)工具把邏輯映射到目標(biāo)器件結(jié)構(gòu)的資源中,決定邏輯的最佳布局,選擇邏輯與輸入輸出功能連接的布線通道進(jìn)行連線,并產(chǎn)生相應(yīng)文件(如配置文件與相關(guān)報(bào)告)。通常可分為如下五個(gè)步驟。

(1)轉(zhuǎn)換:將多個(gè)設(shè)計(jì)文件進(jìn)行轉(zhuǎn)換并合并到一個(gè)設(shè)計(jì)庫(kù)文件中。

(2)映射:將網(wǎng)表中邏輯門(mén)映射成物理元素,即把邏輯設(shè)計(jì)分割到構(gòu)成可編程邏輯陣列內(nèi)的可配置邏輯塊與輸入輸出塊及其它資源中的過(guò)程。

(3)布局與布線:布局是指從映射取出定義的邏輯和輸入輸出塊,并把它們分配到FPGA內(nèi)部的物理位置,通?;谀撤N先進(jìn)的算法,如最小分割、模擬退火和一般的受力方向張弛等來(lái)完成;布線是指利用自動(dòng)布線軟件使用布線資源選擇路徑試著完成所有的邏輯連接。因最新的設(shè)計(jì)實(shí)現(xiàn)工具是時(shí)序驅(qū)動(dòng)的,即在器件的布局布線期間對(duì)整個(gè)信號(hào)通道執(zhí)行時(shí)序分析,因此可以使用約束條件操作布線軟件,完成設(shè)計(jì)規(guī)定的性能要求。在布局布線過(guò)程中,可同時(shí)提取時(shí)序信息形成報(bào)靠。

(4)時(shí)序提?。寒a(chǎn)生一反標(biāo)文件,供給后續(xù)的時(shí)序仿真使用。

(5)配置:產(chǎn)生FPGA配置時(shí)的需要的位流文件。

在實(shí)現(xiàn)過(guò)程中可以進(jìn)行選項(xiàng)設(shè)置。因其支持增量設(shè)計(jì),可以使其重復(fù)多次布線,且每次布線利用上一次布線信息以使布線更優(yōu)或達(dá)到設(shè)計(jì)目標(biāo)。在實(shí)現(xiàn)過(guò)程中應(yīng)設(shè)置默認(rèn)配置的下載形式,以使后續(xù)位流下載正常。

2.5時(shí)序分析

在設(shè)計(jì)實(shí)現(xiàn)過(guò)程中,在映射后需要對(duì)一個(gè)設(shè)計(jì)的實(shí)際功能塊的延時(shí)和估計(jì)的布線延時(shí)進(jìn)行時(shí)序分析;而在布局布線后,也要對(duì)實(shí)際布局布線的功能塊延時(shí)和實(shí)際布線延時(shí)進(jìn)行靜態(tài)時(shí)序分析。從某種程序來(lái)講,靜態(tài)時(shí)序分析可以說(shuō)是整個(gè)FPGA設(shè)計(jì)中最重要的步驟,它允許設(shè)計(jì)者詳盡地分析所有關(guān)鍵路徑并得出一個(gè)有次序的報(bào)告,而且報(bào)告中含有其它調(diào)試信息,比如每個(gè)網(wǎng)絡(luò)節(jié)點(diǎn)的扇出或容性負(fù)載等。靜態(tài)時(shí)序分析器可以用來(lái)檢查設(shè)計(jì)的邏輯和時(shí)序,以便計(jì)算各通中性能,識(shí)別可靠的蹤跡,檢測(cè)建立和保持時(shí)間的配合,時(shí)序分析器不要求用戶產(chǎn)生輸入激勵(lì)或測(cè)試矢量。

雖然Xilinx與Altera在FPGA開(kāi)發(fā)套件上擁有時(shí)序分析工具,但在擁有第三方專門(mén)時(shí)序分析工具的情況下,僅利用FPGA廠家設(shè)計(jì)工具進(jìn)行布局布線,而使用第三方的專門(mén)時(shí)序分析工具進(jìn)行時(shí)序分析,一般FPGA廠商在其設(shè)計(jì)環(huán)境下皆有與第三方時(shí)序分析工具的接口。Synopsys公司的PrimeTIme是一個(gè)很好的時(shí)序分析工具,利用它可以達(dá)到更好的效果。將綜合后的網(wǎng)表文件保存為db格式,可在PrimeTIme環(huán)境下打開(kāi)。利用此軟件查看關(guān)鍵路徑或設(shè)計(jì)者感興趣的通路的時(shí)序,并對(duì)其進(jìn)行分析,再次對(duì)原來(lái)的設(shè)計(jì)進(jìn)行時(shí)序結(jié)束,可以提高工作主頻或減少關(guān)鍵路徑的躚 時(shí)。與綜合過(guò)程相似,靜態(tài)時(shí)序分析也是一個(gè)重復(fù)的過(guò)程,它與布局布線步驟緊密相連,這個(gè)操作通常要進(jìn)行多次直到時(shí)序約束得到很好的滿足。

在綜合與時(shí)序仿真過(guò)程中交互使用PrimeTIme進(jìn)行時(shí)序分析,滿足設(shè)計(jì)要求后即可進(jìn)行FPGA芯片投片前的最終物理驗(yàn)證。

2.6下載驗(yàn)證

下載是在功能仿真與時(shí)序仿真正確的前提下,將綜合后形成的位流下載到具體的FPGA芯片中,也叫芯片配置。FPGA設(shè)計(jì)有兩種配置形式:直接由計(jì)算機(jī)經(jīng)過(guò)專用下載電纜進(jìn)行配置;由外圍配置芯片進(jìn)行上電時(shí)自動(dòng)配置。因FPGA具有掉電信息丟失的性質(zhì),因此可在驗(yàn)證初期使用電纜直接下載位流,如有必要再將燒錄配置芯片中(如Xilinx的XC18V系列,Altera的EPC2系列)。使用電纜下載時(shí)有多種直載方式,如對(duì)Xilinx公司的FPGA下載可以使用JTAG Programmer、Hardware Programmer、PROM Programmer三種方式,而對(duì)Altera公司的FPGA可以選擇JTAG方式或Passive Serial方式。因FPGA大多支持IEEE的JTAG標(biāo)準(zhǔn),所以使用芯片上的JTAG口是常用下載方式。

將位流文件下載到FPGA器件內(nèi)部后進(jìn)行實(shí)際器件的物理測(cè)試即為電路驗(yàn)證,當(dāng)?shù)玫秸_的驗(yàn)證結(jié)果后就證明了設(shè)計(jì)的正確性。電路驗(yàn)證對(duì)FPGA投片生產(chǎn)具有較大意義。

3.多種EDA工具的FPGA設(shè)計(jì)

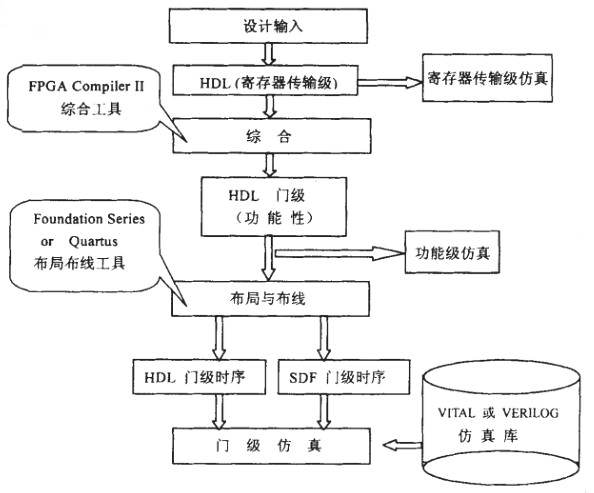

仿真工具M(jìn)odelsim與綜合工具FPGA Compiler II及布線工具Foundation Series或Quartus相配合實(shí)現(xiàn)FPGA設(shè)計(jì)流程圖如圖3所示。

在設(shè)計(jì)輸入階段,因Modelsim僅支持VHDL或Verilog HDL,所以在選用多種設(shè)計(jì)輸入工具時(shí),可以使用文本編輯器完成HDL語(yǔ)言的輸入,也可以利用相應(yīng)的工具以圖形方式完成輸入,但必須能夠?qū)С鰧?duì)應(yīng)的VHDL或Verilog HDL格式。近年來(lái)出現(xiàn)的圖形化HDL設(shè)計(jì)工具,可以接收邏輯結(jié)構(gòu)圖、狀態(tài)轉(zhuǎn)換圖、數(shù)據(jù)流圖、控制流程圖及真值表等輸入方式,并通過(guò)配置的翻譯器將這些圖形格式轉(zhuǎn)化為HDL文件,如Mentor Graphics公司的Renoir,Xilinx公司的Foundation Series都帶有將狀態(tài)轉(zhuǎn)換圖翻譯成HDL文本的設(shè)計(jì)工具。在這方面,Summit公司(現(xiàn)在已經(jīng)合并為Innoveda)的圖形化界面友好程度較高,且可以導(dǎo)出相應(yīng)的HDL格式。

從圖3中可以看到有三處可以由Modelsim進(jìn)行仿真:第一處是寄存器傳輸級(jí)(RTL)仿真,此級(jí)仿真是對(duì)設(shè)計(jì)的語(yǔ)法和基本功能進(jìn)行驗(yàn)證(不含時(shí)序信息);第二處是針對(duì)特定的FPGA廠有技術(shù)的仿真,此級(jí)偽真是在綜合后、實(shí)現(xiàn)前而進(jìn)行的功能級(jí)仿真,功能級(jí)仿真一般驗(yàn)證綜合后是否可以得到設(shè)計(jì)者所需要的正確功能;第三處仿真是門(mén)級(jí)仿真,此級(jí)仿真是針對(duì)門(mén)級(jí)時(shí)序進(jìn)行的仿真,門(mén)級(jí)仿真體現(xiàn)出由于布局布線而產(chǎn)生的實(shí)際延時(shí)。

在RTL仿真階段,應(yīng)該建立一個(gè)測(cè)試臺(tái)。此測(cè)試臺(tái)可以在整個(gè)FPGA流程中進(jìn)行仿真驗(yàn)證(RTL級(jí)、功能級(jí)、時(shí)序門(mén)級(jí))。測(cè)試臺(tái)不但提供測(cè)試激勵(lì)與接收響應(yīng)信息,而且可以測(cè)試HDL仿真流程中的關(guān)鍵功能(如運(yùn)算部件輸出值的正確性等)。測(cè)試臺(tái)的產(chǎn)生可以直接使用文本編程得到,也可以使用圖形化工具輸入,再由軟件翻譯為HDL格式,例如使用HDL Bencher軟件利用其良好的波形輸入界面輸入測(cè)試激勵(lì),再由其自動(dòng)轉(zhuǎn)化為HDL格式而得到。

在功能級(jí)仿真階段,一般驗(yàn)證綜合后是否仍與RTL級(jí)仿真結(jié)果相同。

圖3 實(shí)現(xiàn)FPGA設(shè)計(jì)流程圖

在門(mén)級(jí)仿真階段,由于已經(jīng)針對(duì)具體的FPGA廠家技術(shù)進(jìn)行了功能級(jí)仿真,因此可以通過(guò)布局布線得到標(biāo)準(zhǔn)延格式下的時(shí)序信息進(jìn)行門(mén)級(jí)仿真。

Mentor Graphics公司的Modelsim是業(yè)界較好的仿真工具,其仿真功能強(qiáng)大,且圖形化界面友好,而且具有結(jié)構(gòu)、信號(hào)、波形、進(jìn)程、數(shù)據(jù)流等窗口。將FPGA設(shè)計(jì)(以HDL方式)輸入后進(jìn)行編譯即可進(jìn)行前仿真,其最新版本Modelsim SE/Plus 5.5支持VHDL與Verilog HDL混合仿真。在仿真時(shí)可以編寫(xiě)HDL激勵(lì)文件或執(zhí)行組模式方式。組模式方式類似批處理方式,可以連續(xù)執(zhí)行事先在文件中寫(xiě)好的多個(gè)執(zhí)行命令,這對(duì)重新仿真或重復(fù)執(zhí)行多個(gè)命令特別有效。在仿真過(guò)程中可以執(zhí)行性能分析與代碼覆蓋分析。性能分析在程序代碼執(zhí)行過(guò)程中可以分析出各部分代碼執(zhí)行時(shí)占用整個(gè)執(zhí)行時(shí)間的百分率。在此信息下,設(shè)計(jì)者可以找到設(shè)計(jì)的瓶頸并通過(guò)優(yōu)化代碼減少仿真時(shí)間。代碼覆蓋分析可以使設(shè)計(jì)者確切知道在測(cè)試臺(tái)上正在進(jìn)行的代碼位置,以方便設(shè)計(jì)者調(diào)試。

由Modelsim進(jìn)行仿真,需要導(dǎo)出VHDL或Verilog HDL網(wǎng)表。此網(wǎng)表是由針對(duì)特定FPGA器件的基本單元組成的。這些基本單元在FPGA廠家提供的廠家?guī)熘泻衅涠x和特性,且廠家一般提供其功能的VHDL或Verilog VDL庫(kù)。因此,在Modelsim下進(jìn)行仿真,需要設(shè)置廠家?guī)煨畔?。如使用Altera公司的Apex20ke系列,需要將Apex20ke_atoms.v(或.vhd)與Apex20ke_component.v文件設(shè)置或編譯到工程項(xiàng)目的對(duì)應(yīng)庫(kù)中。除網(wǎng)表外,還需要布局布線輸出的標(biāo)準(zhǔn)延時(shí)文件(sdf),將sdf文件加入仿真可以在窗口化界面設(shè)置加入,或通過(guò)激勵(lì)指定。如使用Verilog HDL時(shí)加入反標(biāo)語(yǔ)句$sdf_annotate(“”,Top)通過(guò)參數(shù)路徑指定即可。

在綜合階段,應(yīng)利用設(shè)計(jì)指定的約束文件將RTL級(jí)設(shè)計(jì)功能實(shí)現(xiàn)并優(yōu)化到具有相等功能且具有單元延時(shí)(但不含時(shí)序信息)的基本器件中,如觸發(fā)器、邏輯門(mén)等,得到的結(jié)果是功能獨(dú)立于FPGA的網(wǎng)表。它不含時(shí)序信息,可作為后續(xù)的布局布線使用。使用FPGA Compiler II進(jìn)行綜合后可以導(dǎo)出EDIF網(wǎng)絡(luò)。

在實(shí)際階段,主要是利用綜合后生成的EDIF網(wǎng)表并基于FPGA內(nèi)的基本器件進(jìn)行布局布線??梢岳貌季€工具Foundation Series選用具體器件(如Virtex系列器件)進(jìn)行布局布線加以實(shí)現(xiàn),也可以使用布線工具Quartus選用Apex20ke系列器件進(jìn)行布局布線加以實(shí)現(xiàn),同時(shí)輸出相應(yīng)的VHDL或Verilog HDL格式,以便在Modelsim下進(jìn)行仿真。

結(jié)束語(yǔ)

以上就是采用多種EDA工具的FPGA設(shè)計(jì)介紹了。在數(shù)字系統(tǒng)設(shè)計(jì)的今天,采用多種EDA工具進(jìn)行處理,同時(shí)使用FPGA快速設(shè)計(jì)專用系統(tǒng)或作為檢驗(yàn)手段,已經(jīng)成為數(shù)字系統(tǒng)設(shè)計(jì)中不可或缺的一種方式,了解并熟悉其設(shè)計(jì)流血應(yīng)成為現(xiàn)今電子工程師的一種必備知識(shí)。

電話:18923864027(同微信)

QQ:709211280

〈烜芯微/XXW〉專業(yè)制造二極管,三極管,MOS管,橋堆等,20年,工廠直銷(xiāo)省20%,上萬(wàn)家電路電器生產(chǎn)企業(yè)選用,專業(yè)的工程師幫您穩(wěn)定好每一批產(chǎn)品,如果您有遇到什么需要幫助解決的,可以直接聯(lián)系下方的聯(lián)系號(hào)碼或加QQ/微信,由我們的銷(xiāo)售經(jīng)理給您精準(zhǔn)的報(bào)價(jià)以及產(chǎn)品介紹