LVDC輸入電平

低壓差分發信(LVDS)系統(見圖1)運行在高數據率。這些系統在無噪聲干擾和VCC穩定性方面非同一般,它們為兩點間快速獲得數據提供一種簡易方法。LVDS系統其中一個設計參量是提供給LVDS驅動器輸入的信號電平。重要的是在閾值電平附近(此時驅動呂在狀態間開關轉換輸出)使LVDS驅動器的高電平和低電平輸入保持平衡(對稱)。

非對稱輸入影響

非對稱輸入影響很容易看到。如圖2所示。當輸入不在驅動器VTHRES開關轉換電平中心時,接收器輸出明顯出現失真。

LVDS電平規范

到3.3V LVDS線驅動器的輸入電平對于邏輯0為0.0VDC到0.8VDC、對于邏輯1為2.0VDC到3.0VDC。0.8VDC和2.0VDC之間的輸入電平公平定義,這意味著驅動的開關轉換閾值電平也未定義,但這是不難確定的。加一時鐘信號到系統并調節輸入電平VIH和VIL,監視50%占空因數的接收器輸出,得到圖3所示的數據。圖3中所示的VTHRES值是從VIH和VIL輸入電平計算的。注意,這可看做為輸入靈敏度,不僅僅適合LVDS驅動器,也適合整個LVDS系統。計算結果表明接近1.35VDC的VTHRES與數據(或時鐘)率無關。

幅度和補償

圖4示出當輸入電平正在輸入閾值中心時的驅動器輸出。通道1波形(接近52%占空因數)是VIH=2.35VDC和VIL=0.35V時的驅動器輸出,這靠近1.35V閾值附近的中心。注意,圖4中通道2波形(接近60%占空因數)。這示出對輸入VIH=2.5VDC和VIL=0.5VDC的驅動器輸出響應。這仍然為2.0Vpp幅度,但中心在1.5VDC。結果是在輸出稍微"不對稱"。邏輯1寬度增加大約640psec,這是靠犧牲邏輯0的寬度。

當采用脈沖分布時,這種不對稱不是問題,因為上升和下降沿是清楚和穩定的。高速時鐘信號是相當滿意的方波(50%占空因數),但當傳送數據(此例為200Mbps)時這種不對稱可能成為問題。在200Mbps,每個數據位應為5ns寬,圖4結果示出通道2波形0位為4.36ns(5.0ns~0.64ns)寬、1位為5.64ns(5.0ns+0.64ns)寬。0和1之間的差為1.28ns,對于VIH=2.5VDC和VIL=0.5VDC,這很符合規格要求。

只要輸入處在輸入閾值中心附近,其輸出將保持正確的占空因數和位寬度。在圖5中,通道1是當輸入幅度為1.5VDC、補償為1.35VDC(VIH=2.1VDC,VIL=0.6VDC)時的驅動器輸出。通道2是輸入幅度降到0.5VDC、補償1.35VDC不變化(現在VIH=1.85V,VIL=0.85V)時的驅動器輸出。對于傳播延遲或驅動器占空因數漂移沒有明顯的不同。這些輸入電平不滿足LVDS規格,但工作很好。

為什么占空因數變化

此問題的答案示于圖6。在圖6(A)中,輸出電平在閾值中心之上,這導致正占空因數增加。在圖6(B)中,輸入處在閾值中心處,使占空因數為50%/50%。在圖6(C)中,輸入電平中心低于閾值,導致正占空因數減小。圖6(C)也示出驅動器對輸入信號的響應。對于NR2數據流、占空因數的變化轉換為0和1寬度之間的差。

閾值調節

閾值不能調節,但輸入電平可調節。圖3中數據表明:甚至在高發信率,LVDS驅動器的輸入靈敏度大約為300mV(小于較慢的發信率)。這意味著在驅動器輸入加上一個電阻分壓器來調節輸入信號是可能的。

筆者用VIH=3.5V和VIL=0.5VDC(幅度=3.0V,補償=2.0VDC)仿真100MHz時鐘分配系統。為使補償電壓降到接近驅動器的閾值電壓,加入圖7所示的電阻器分壓器網絡。

該分壓器使補償從2.0V降到1.4V,非常接近于驅動器閾值電壓。它也使輸入幅度降低30%,使VIH=2.46VDC和VIL=0.35VDC。

在任何傳輸系統中,到驅動器的輸入電平是影響線接收器信號輸出質量的因素之一。對于任何驅動器,RS-422,LVDS,SCSI等都是這樣。

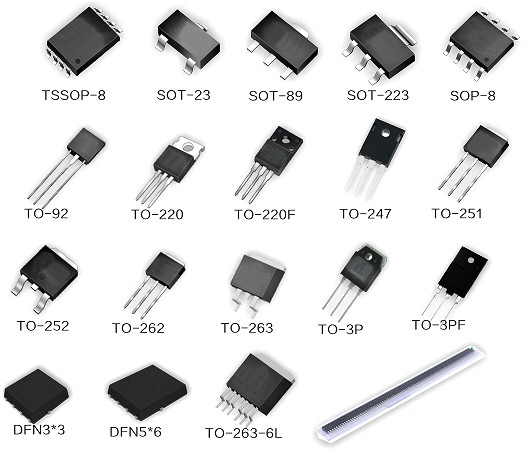

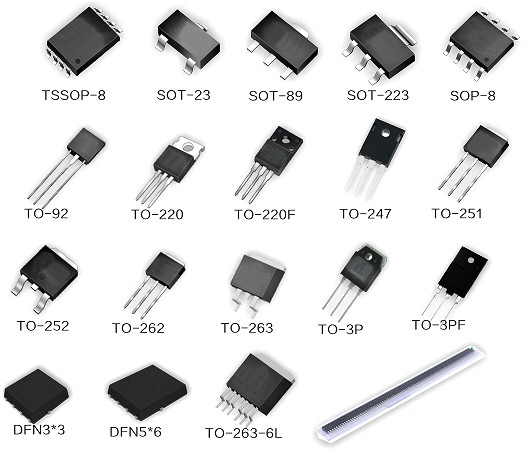

烜芯微專業制造二極管,三極管,MOS管,橋堆等20年,工廠直銷省20%,4000家電路電器生產企業選用,專業的工程師幫您穩定好每一批產品,如果您有遇到什么需要幫助解決的,可以點擊右邊的工程師,或者點擊銷售經理給您精準的報價以及產品介紹

烜芯微專業制造二極管,三極管,MOS管,橋堆等20年,工廠直銷省20%,4000家電路電器生產企業選用,專業的工程師幫您穩定好每一批產品,如果您有遇到什么需要幫助解決的,可以點擊右邊的工程師,或者點擊銷售經理給您精準的報價以及產品介紹