電阻簡介

電阻(Resistance,通常用“R”表示),是一個物理量,在物理學中表示導體對電流阻礙作用的大小。導體的電阻越大,表示導體對電流的阻礙作用越大。不同的導體,電阻一般不同,電阻是導體本身的一種特性。電阻將會導致電子流通量的變化,電阻越小,電子流通量越大,反之亦然。而超導體則沒有電阻。

電阻的本質與單位表示

(一)本質

正常金屬有電阻,是因為載流子會受到散射而改變動量。散射的中心就是聲子,缺陷,雜質原子等。在超導情況下,組成庫伯對的電子不斷地相互散射,但這種散射不影響庫伯對質心動量,所以有電流通過超導體時庫伯對的定向移動不受阻礙,沒有電阻。

(二)單位表示

導體的電阻通常用字母R表示,電阻的單位是歐姆(ohm),簡稱歐,符號是Ω(希臘字母,讀作Omega),1Ω=1V/A。比較大的單位有千歐(kΩ)、兆歐(MΩ)(兆=百萬,即100萬)。

KΩ(千歐), MΩ(兆歐),他們的換算關系是:兩個電阻并聯式也可表示為:1TΩ=1000GΩ;1GΩ=1000MΩ;1MΩ=1000KΩ;1KΩ=1000Ω(也就是一千進率)

功率MOSFET的導通電阻詳解

電阻值的測量通常比較簡單。但是,對于非常小阻值的測量,我們必須謹慎對待我們所做的假定。對于特定的幾何形狀,如電線,Kelvin方法是非常精確的。可以使用類似的方法來測量均勻樣本的體電阻率和面電阻率,但是所使用的公式不同。在這些情況下,必須考慮探針間距和樣本厚度。僅僅運用Kelvin法本身無法保證精度。如果布局和連接數發生變化,就很難精確地預測非均勻幾何形狀的電阻。

MOSFET最重要的特性之一就是漏極到源極的導通電阻(RDS(on))。在封裝完成之后測量RDS(on)很簡單,但是以晶圓形式測量該值更具有其優勢。

(一)功率MOSFET的導通電阻-晶圓級測量

為了保證Kelvin阻值測量的精度,需要考慮幾項重要的因素:(1)待測器件(DUT)的幾何形狀;(2)到器件的接線;(3)材料的邊界;(4)各種材料(包括接線)的體電阻率。

一種測量RDS(on)的典型方法是在卡盤(Chuck)和接觸晶圓頂部的探針之間產生電流。另一種方法是在晶圓的背面使用探針來代替卡盤。這種方法可以精確到2.5mΩ。

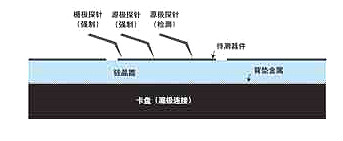

一種較大的誤差來源于晶圓和卡盤之間的接觸(如圖1所示)。因為卡盤上以及晶圓背面粗糙不平,所以只有在個別點進行電氣連接。晶圓和卡盤之間的接觸電阻的數值足以給RDS(on)的測量引入較大的誤差。僅僅重新放置卡盤上晶圓的位置就會改變接觸區域并影響RDS(on)的測量結果。

圖1 典型的測量結構,橫截面視圖

另一種測量偏差來源是探針的布局。如果移動了強制電流探針,電流的分布模式將發生變化。這會改變電壓梯度模式,而且會改變電壓檢測探針處的電壓。

(二)功率MOSFET的導通電阻-相鄰晶粒方法

需要的設備包括:(1)帶有6個可用探針的探針臺;(2)電壓計;(3)電流源。將晶圓和導電的卡盤隔離開這一點非常重要。如果晶圓與卡盤存在接觸,那么這種接觸將造成電流以平行于基底的方式流動,改變了測量結果。可以用一張紙將晶圓和卡盤隔離開。

到漏極的連接是通過在待測器件的另一側使用相鄰的完全相同的器件來實現的。內部晶圓結構要比晶圓和卡盤之間的連接牢固得多。因此,相鄰晶粒方法要比傳統的RDS(on)測量方法精確得多。

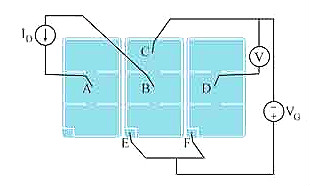

圖2顯示了測量的結構。3個MOSFET和6個探針均在圖中顯示出來,電接觸則示意性地畫出。中間的MOSFET是待測器件。

圖2 RDS(on)測量結構

顯示的極性屬于N溝道MOSFET。漏極電流受限于探針的電流傳輸能力。左側的MOSFET的作用是在待測器件的漏極側施加電流。待測器件右側的MOSFET用于測量漏極電壓。

在MOSFET中,如果柵極開啟,而且漏極到源極之間沒有電流,那么漏極和源極的電壓相等。這種方法就利用這個原理來測量探針D上的漏極電壓。

柵極偏壓被連接在探針C和E之間。如果連接在探針B和E之間,那么探針B和源極焊盤之間的電壓降會降低待測器件上的實際柵極電壓。因為在RDS(on)測量過程中沒有電流通過,所以探針C上不存在電壓降。

相鄰晶粒方法確實需要右側的MOSFET(在探針D和F之間)處于工作狀態。如果這個晶粒上的柵極和源極被短路,那么測量結果可能不正確。

RDS(on)的取值是通過計算Vdc/IAB得到的,但是也可以得到更加精確的RDS(on)取值。

(三)功率MOSFET的導通電阻-FEA輔助確定RDS(on)測量值

盡管相鄰晶粒法很精確,但是它并不能給出RDS(on)完全精確的測量值。為了得到僅由有源區貢獻的RDS(on),可以將測量結果與仿真進行對比。有限元分析(FEA)軟件可以用來為測量結構建模。一旦建立了有源區電阻和RDS(on)測量值之間的關系,就可以根據測量結果確定有源區的電阻。

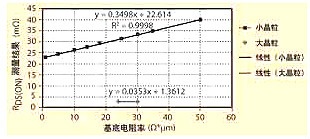

仿真模型是3個MOSFET和晶圓的一部分的三維表示。在有限元模型中,有源區電阻是已知的。FEA軟件用來對測試結構建模并計算RDS(on)測量結果。仿真過程進行兩次,使用兩個不同的有源區電阻值來計算結果。因為響應的線性相當好,所以電阻值是任意選取的。對每種晶粒的尺寸,這種仿真只需要進行一次。利用仿真測量結果和實際有源區的電阻之間的關系,可以得到一個公式,用來根據相鄰晶粒方法的測量值計算有源區電阻。

(四)功率MOSFET的導通電阻-相鄰晶粒方法2

有幾項因素會給測量引入誤差。最重要的因素是探針的位置以及基底的電阻率。

從仿真結果可以看出,有些因素對測量結果的影響非常小。基底的厚度通常是200μm。厚度從175μm變化到225μm只會給RDS(on)帶來1%的誤差(仿真的測量結果)。同樣,背墊金屬表面電阻的變化對結果的影響也不會超過1%。仿真得到的一項驚人的結果表明,頂部金屬厚度和電阻率對結果的影響也可以忽略不計。

基底電阻率的變化會給RDS(on)測量結果帶來線性響應。圖3顯示了遠遠超出實際基底正常分布的基底電阻率。這樣做是為了顯示響應是線性的。

圖3 由于基底電阻率造成的仿真結果的誤差

探針在待測器件上的擺放位置必須保持一致。探針位置的變化會造成測量結果的變化。待測器件左側和右側器件上探針的位置(見圖2中的A和D)也會影響測量結果,但是影響沒有前者大。造成這種測量誤差的原因在于頂部金屬的表面電阻大于0。

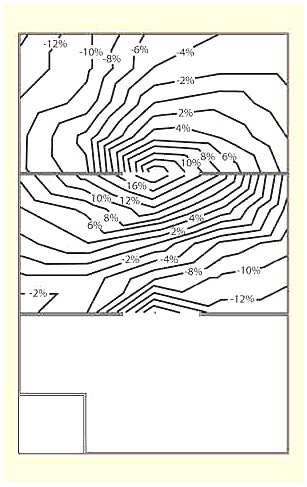

將探針B或C從源極焊盤中心向邊緣移動會導致較大的誤差。圖4顯示了移動探針B或C所產生的誤差。每條線表示RDS(on) 2%的誤差。在繪制這張圖時,使用了5μm×5μm的網格。每次只移動一個探針的位置。

圖4 探針位置所引起的誤差

相鄰晶粒方法是一種成本低廉、精確地以晶圓形式測量MOSFET有源區的RDS(on)的方法。它在檢測不同批次晶圓的差別方面非常有用。

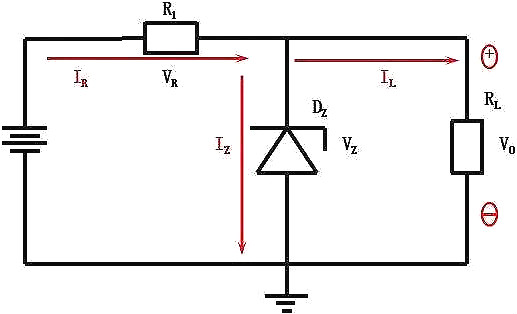

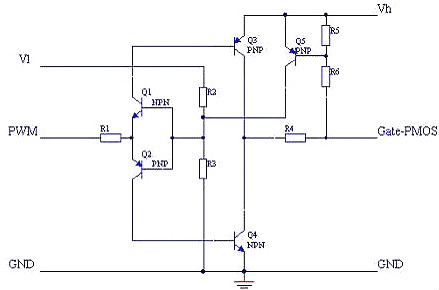

MOSFET的導通電阻的作用

mos管導通電阻,一般在使用MOS時都會遇到柵極的電阻選擇和使用問題,但有時對這個電阻很迷茫,現介紹一下它的作用:

1.是分壓作用

2.下拉電阻是盡快泄放柵極電荷將MOS管盡快截止

3.防止柵極出現浪涌過壓(柵極上并聯的穩壓管也是防止過壓產生)

4.全橋柵極電阻也是同樣機理,盡快泄放柵極電荷,將MOS管盡快截止。避免柵極懸空,懸空的柵極MOS管將會導通,導致全橋短路

5.驅動管和柵極之間的電阻起到隔離、防止寄生振蕩的作用

降低高壓MOSFET的導通電阻的原理與方法

1.不同耐壓的MOS管的導通電阻分布。不同耐壓的MOS管,其導通電阻中各部分電阻比例分布也不同。如耐壓30V的MOS管,其外延層電阻僅為總導通電阻的29%,耐壓600V的MOS管的外延層電阻則是總導通電阻的96.5%。

由此可以推斷耐壓800V的MOS管的導通電阻將幾乎被外延層電阻占據。欲獲得高阻斷電壓,就必須采用高電阻率的外延層,并增厚。這就是常規高壓MOS管結構所導致的高導通電阻的根本原因。

2.降低高壓MOS管導通電阻的思路。增加管芯面積雖能降低導通電阻,但成本的提高所付出的代價是商業品所不允許的。引入少數載流以上兩種辦法不能降低高壓MOS管的導通電阻,所剩的思路就是如何將阻斷高電壓的低摻雜、高電阻率區域和導電通道的高摻雜、低電阻率分開解決。如除導通時低摻雜的高耐壓外延層對導通電阻只能起增大作用外并無其他用途。

這樣,是否可以將導電通道以高摻雜較低電阻率實現,而在MOS管關斷時,設法使這個通道以某種方式夾斷,使整個器件耐壓僅取決于低摻雜的N-外延層。基于這種思想,1988年INFINEON推出內建橫向電場耐壓為600V的COOLMOS管,使這一想法得以實現。內建橫向電場的高壓MOS管的剖面結構及高阻斷電壓低導通電阻的示意圖如圖所示。

與常規MOS管結構不同,內建橫向電場的MOS管嵌入垂直P區將垂直導電區域的N區夾在中間,使MOS管關斷時,垂直的P與N之間建立橫向電場,并且垂直導電區域的N摻雜濃度高于其外延區N-的摻雜濃度。

當VGS<VTH時,由于被電場反型而產生的N型導電溝道不能形成,并且D,S間加正電壓,使MOS管內部PN結反偏形成耗盡層,并將垂直導電的N區耗盡。這個耗盡層具有縱向高阻斷電壓,如圖(b)所示,這時器件的耐壓取決于P與N-的耐壓。因此N-的低摻雜、高電阻率是必需的。

烜芯微專業制造二極管,三極管,MOS管,橋堆等20年,工廠直銷省20%,1500家電路電器生產企業選用,專業的工程師幫您穩定好每一批產品,如果您有遇到什么需要幫助解決的,可以點擊右邊的工程師,或者點擊銷售經理給您精準的報價以及產品介紹