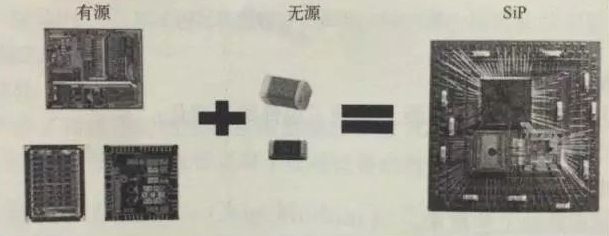

SiP(系統級封裝,System in Package)是在系統芯片(SoC)設計理念基礎發展出來的一種集成電路封裝技術,指將多顆芯片或單芯片與電阻器、電容器、連接器、晶振、天線等被動組件封裝在一起,構成更為一個具有一定功能的電路系統。

SIP對不同芯片、電子元件進行并排或疊加形成單個標準封裝

從一定程度講,SiP是SoC技術在納米時代的裂變。隨著SoC制程從微米進入納米,單一集成電路芯片內所能容納的晶體管數目愈來愈多,業界通過提高SoC整合度滿足用戶對低功耗、低成本及高效能的要求。但是當半導體制程進入納米時代后,SoC所面臨的各種問題,如制程微縮瓶頸,成本愈來愈大,異質(Heterogeneous)整合困難,產品生命周期變短等,這為SiP技術帶來了嶄新的發展機會。

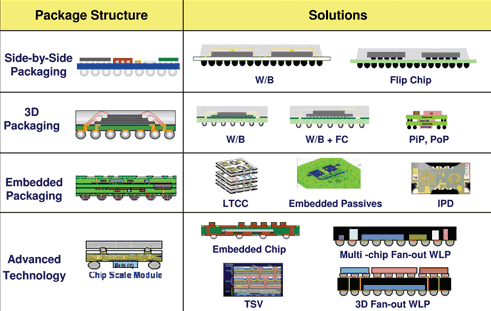

概念上,SiP包括了多芯片模組(Multi-chip Module;MCM)技術、多芯片封裝(Multi-chip Package;MCP)技術、芯片堆疊(Stack Die)、PoP(Package on Package)、PiP(Package in Package),以及將主/被動組件內埋于基板(Embedded Substrate)等技術。

在結構上,MCM屬于二維的2D構裝,而MCP、Stack Die、PoP、PiP等則屬于立體的3D構裝;由于3D更能符合小型化、高效能等需求,因而在近年來備受業界青睞。

工藝上,SiP集成電路封裝互連技術(Interconnection)多以打線接合(Wire Bonding)為主,少部分還采用覆晶技術(Flip Chip),或是Flip Chip搭配Wire Bonding作為與Substrate(IC載板)間的互連。但以Stack Die(堆疊芯片)為例,上層的芯片仍需藉由Wire Bonding來連接,當堆疊的芯片數增加,越上層的芯片所需的Wire Bonding長度則將越長,也因此影響了整個系統的效能;而為了保留打線空間的考慮,芯片與芯片間則需適度的插入Interposer,造成封裝厚度的增加。

SiP技術特點

系統封裝(SiP)技術在現有集成電路封裝中并非高困難度的制程,因為各種功能芯片利用集成電路封裝技術整合,除考慮封裝體的散熱處理外,功能芯片組構可以將原本離散的功能設計或組件,整合在單一芯片,不僅可以避免設計方案被抄襲復制,也能透過多功能芯片整合的優勢讓最終產品更具市場競爭力,尤其在產品的體積、功耗與成本上都能因為SiP技術而獲得改善。

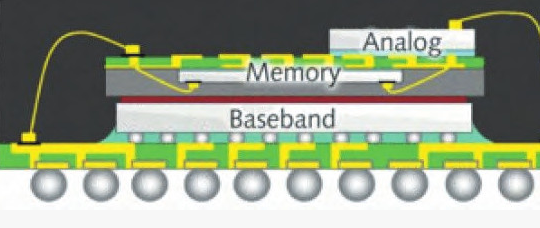

最基礎的SIP封裝結構

SiP元器件若設計規劃得當,已可相當于一系統載板的相關功能芯片、電路的總和,而依據不同的功能芯片進行系統封裝,可以采簡單的Side by Side芯片布局,也可利用相對更復雜的多芯片模組MCM(Multi-chip Module)技術、多芯片封裝MCP(Multi-chip Package)技術、芯片堆疊(Stack Die)、PoP(Package on Package)、PiP(Package in Package)等不同難度與制作方式進行系統組構。也就是說,在單一個封裝體內不只可運用多個芯片進行系統功能建構,甚至還可將包含前述不同類型器件、被動組件、電路芯片、功能模組封裝進行堆疊,透過內部連線或是更復雜的3D IC技術整合,構建成更為復雜的、完整的SiP系統功能。

而在SiP整合封裝中,關鍵的技術就在于SiP封裝體中的芯片或功能模組的芯片內互連技術(Interconnection),在一般簡單形式或是對芯片體積要求不高的方案中,運用打線接合(Wire Bonding)即可滿足多數需求,而打線接合形式芯片多用Side by Side并列布局為主,當功能芯片數量多時,芯片的占位面積就會增加,而若要達到SiP封裝體再積極微縮設計,就可改用技術層次更高的覆晶技術(Flip Chip)或是Flip Chip再搭配打線接合與IC載板(Substrate)之間進行互連。

基本上堆疊芯片(Stack Die)的作法在上層的芯片或模塊仍然需要透過打線接合進行連接,但若碰到SiP的整合芯片、功能模塊數量較多時,即堆疊的芯片、功能模組數量增加,這會導致越是設于SiP結構上層的芯片、模塊所需要的打線連接電子線路長度將因此增長,傳輸線路拉長對于高時脈運作的功能模塊會產生線路雜訊或是影響了整體系統效能;至于SiP在結構上為了預留Wire Bonding的打線空間,對芯片與芯片或是功能模塊與功能模塊間插入的Interposer處理,也會因為這些必要程序導致SiP最終封裝成品的厚度增加。

典型SiP封裝方案

隨著集成電路封裝技術不斷演進,芯片或功能模塊的裸晶本身制程,已從微米制程升級至納米等級,這代表單一個功能芯片或功能模塊可以越做越小,也代表SiP的功能可因而得到倍數的成長,甚至還能游刃有余地維持相同的封裝體尺寸。

SiP應用優勢

目前,SiP封裝已經成為輕薄電子產品首選的集成電路封裝形式。

首先,SiP可利用封裝技術讓整合設計更具效率,也就是說SiP可在單一封裝體內裝多組功能芯片,例如單一SiP若整合兩組功能芯片,使用堆疊設計可以在相同芯片占位面積設置雙芯片功能,若是三個功能芯片構裝,則可以在單一芯片略大的體積設置多芯片功能。

其次,SiP構裝芯片的設計驗證會比同樣多功能芯片整合的SoC設計方案更簡單許多,基本上這些功能獨立的芯片皆已可透過既有的驗證流程確認功能完整性,而在SiP制程中僅針對芯片與芯片、功能模塊與功能模塊的內部連線在封裝后是否正常無誤進行驗證,大幅減少設計流程與驗證成本。

而SoC卻需要透過版圖布局/布線,不僅在設計流程與負荷相對復雜,在后期的芯片驗證調校成本也相對較高,兩者相較SiP在爭取產品上市時間有絕對優勢。同時,SiP的優點還有可以結合不同功能芯片、功能模塊,在面對異質芯片構裝方面可以極具彈性,在封裝體內還可設置被動組件,甚至集成天線模塊進封裝體,芯片的封裝成果可以自成一套電子系統,實現嵌入式無源組件的設計方案組合。

第三,SiP也可大幅減低系統開發成本,因為相關的電子回路都可以透過封裝體內的線路與組件布局進行整合,如此一來不僅節省了SiP終端元器件本身的占位空間,也能把部分電路載板的關鍵線路、零組件并入SiP封裝體中,極度簡化PCB電路板的復雜度與面積,成本與驗證程序可獲得大幅優化。

另外,高度集成電路封裝整合提升產品抗機械、抗化學腐蝕能力SiP也具備極好的抗機械、抗化學腐蝕能力,因為相關電路都以封裝體整個包覆起來,可增加電路載板的抗機械應力、抗化學腐蝕能力,同時提高了電子系統的可靠性。

烜芯微專業制造二極管,三極管,MOS管,橋堆等20年,工廠直銷省20%,1500家電路電器生產企業選用,專業的工程師幫您穩定好每一批產品,如果您有遇到什么需要幫助解決的,可以點擊右邊的工程師,或者點擊銷售經理給您精準的報價以及產品介紹