漏極電流上升和下降太快會在地線和電源線上引起較大的 Ldi/dt 尖峰電壓并在鄰近的線路或節點上輯合出大的 CdV/dt j良涌電流。

由此引出的問題是,為了盡可能縮短漏極電流的上升時間 ,具體需要多大的柵極電壓上升速度 。圖 9.3b和圖 9.3d 的傳輸特性曲線中給出了答案 。

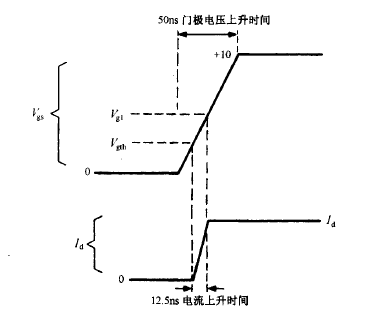

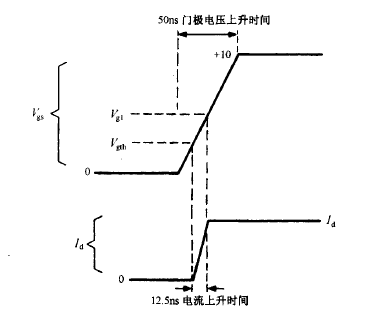

對于MOSFET管,漏極電流從0上升到Id的時間對應于柵極電壓從值電壓比上升到 Vg1 的時間,如圖9.3b所示。柵極電壓從0上升到闕值( 約為 2.5V ) 的時間為 MOSFET 管的導通延遲時間 。漏極電流導通速度并不能像雙極型晶體管那樣通過在輸入端施加過驅動來如速(見8.2節和圖8.2 (b) 。

另外,MOSFET沒有存儲時間 ,只存一個關斷延遲時間 。關斷延遲時間是柵極電壓從最高電壓(約為OV ) 下降到電壓 Vd1 圖 9.3 b所需的時間 。在這個時間段內漏極電流保持不變 ,當柵極電壓下降到 Vd1 時,MOS管開始關斷 。所以漏極電流F降時間是柵極電壓從 Vd1下降到闊值比的時間。

下面討論 MTM7N45 管從關斷狀態到漏極電流Id上升到 2.5A 的導通過程。在柵極電壓 從ov上升至2.5V的50ns 時間里,漏極電流Id為 ov ,如圖9.3 b所示。隨后在柵極電壓升到 5V 的過程中,漏極電流Id 將逐漸從 OA 上升至 2.5A 。

因此,若柵極電壓從ov 上升至 IOV 需要 50ns,則漏極電流從 OA 上升至 2.5A 的時間約 為 ( 2.5+10 )×50=12.Sns ,如圖 9.5 所示。這樣 ,柵極驅動電壓為 IOV 的MOSFET 管的導通時間是漏極開路電流導通時間的 2 3 倍。這是因為漏極電流的上升時間僅僅是柵極電壓上升時間的一小部分。柵極電流只需要為前面計算值的 3/1,2/1 就可以了。

圖若柵極電壓上升時間為 50ns ,則漏極電流上升時間為 12.5ns。柵極電壓從 ov 上升到 2.5V 的闕 值電壓的時間只是一個延遲時間 。當柵極電壓達到 5 7V 時,大部分漏極電流已經建立起來。

烜芯微專業制造二極管,三極管,MOS管,橋堆等20年,工廠直銷省20%,1500家電路電器生產企業選用,專業的工程師幫您穩定好每一批產品,如果您有遇到什么需要幫助解決的,可以點擊右邊的工程師,或者點擊銷售經理給您精準的報價以及產品介紹