COMS集成電路是互補對稱金屬氧化物半導體(Complementary symmetry metal oxide semiconductor)集成電路的英文縮寫,電路的許多基本邏輯單元都是用增強型PMOS晶體管和增強型NMOS管按照互補對稱形式連接的,靜態功耗很小。COMS電路的供電電壓電壓波動允許±10,當輸出電壓高于VDD-0.5VVDD范圍比較廣在+5--+15V均能正常工作,時為邏輯1,輸出電壓低于VSS+0.5V(VSS為數字地)為邏輯0,扇出數為10--20個COMS門電路.

輸出L:<0.1*Vcc;H:>0.9*Vcc

輸入L:<0.3*Vcc;H:>0.7*Vcc

由于CMOS電源采用12V,則輸入低于3.6V為低電平,噪聲容限為1.8V,高于3.5V為高電平,噪聲容限高為1.8V。比TTL有更高的噪聲容限。

輸出高電平和輸出低電平:Uoh≈Vcc,Uol≈GND,

輸入高電平和輸入低電平:Uih≥0.7Vcc,Uil≤0.2Vcc

由上面可知,在同樣5V電源的電壓情況下,CMOS電路可以直接驅動TTL,而TTL電路不能直接驅動CMOS電路,故TTL電路驅動CMOS電路需上拉電阻。

3.3V CMOS可以 直接驅動5V的TTL電路。

(當然上面是一般情況,具體還是要查看所用芯片的datasheet,只要在用的時候注意就行)

比較:A:TTL電路是電流控制器件、CMOS電路是電壓控制器件

B:TTL電路的速度快,傳輸延遲短(5-10ns)但是功耗大

CMOS電路的速度慢,傳輸延遲長(25-50ns),但功耗低,CMOS電路本身的功耗與輸入信號的脈沖頻率有關,頻率越高,芯片越熱,這是正常現象。

二、COMS電路的鎖定效應

COMS電路由于輸入太大的電流,內部的電流急劇增大,除非切斷電源,電流一直在增大。這種效應就是鎖定效應。當產生鎖定效應時,COMS的內部電流能達到40mA以上,很容易燒毀芯片。

防御措施:

1)在輸入端和輸出端加鉗位電路,使輸入和輸出不超過不超過規定電壓。

2)芯片的電源輸入端加去耦電路,防止VDD端出現瞬間的高壓。

3)在VDD和外電源之間加線流電阻,即使有大的電流也不讓它進去。

4)當系統由幾個電源分別供電時,開關要按下列順序:開啟時,先開啟COMS電路得電源,再開啟輸入信號和負載的電源;關閉時,先關閉輸入信號和負載的電源,再關閉COMS電路的電源。

三、CMOS電平接口

我們對它也不陌生,也是經常和它打交道了,一些關于CMOS的半導體特性在這里就不必啰嗦了。許多人都知道的是,正常情況下CMOS的功耗和抗干擾能力遠優于TTL。但是鮮為人知的是,在高轉換頻率時,CMOS系列實際上卻比TTL消耗更多的功率。

由于CMOS的工作電壓目前已經可以很小了,有的FPGA內核工作電壓甚至接近1.5V,這樣就使得電平之間的噪聲容限比TTL小了很多,因此更加加重了由于電壓波動而引發的信號判斷錯誤。

眾所周知,CMOS電路的輸入阻抗是很高的,因此,它的耦合電容容量可以很小,而不需要使用大的電解電容器了。由于CMOS電路通常驅動能力較弱,所以必須先進行TTL轉換后再驅動ECL電路。

此外,設計CMOS接口電路時,要注意避免容性負載過重,否則的話會使得上升時間變慢,而且驅動器件的功耗也將增加(因為容性負載并不耗費功率)。

四、COMS電路的使用注意事項

1)COMS電路時電壓控制器件,它的輸入總抗很大,對干擾信號的捕捉能力很強。所以,不用的管腳不要懸空,要接上拉電阻或者下拉電阻,給它一個恒定的電平。

2)輸入端接低內阻的信號源時,要在輸入端和信號源之間要串聯限流電阻,使輸入的電流限制在1mA之內。

3)當接長信號傳輸線時,在COMS電路端接匹配電阻。

4)當輸入端接大電容時,應該在輸入端和電容間接保護電阻。電阻值為R=V0/1mA.V0是外界電容上的電壓。

5)COMS的輸入電流超過1mA,就有可能燒壞COMS。

五、CMOS的趨勢

進入2000年后,電子電路低電壓化的步伐加快了。這與電子設備的信號處置從模仿向數字轉移有親密的關系。像CG(ComputerGraphic,計算機圖形)那樣,進一步以高速度、高密度(3D,MPEG2,5.lch環繞平面聲等)、而且用電池驅動的筆記本電腦停止編輯、閱覽。像數碼照相機(百萬像素&長時間電池)那樣,請求更低的功率耗費。

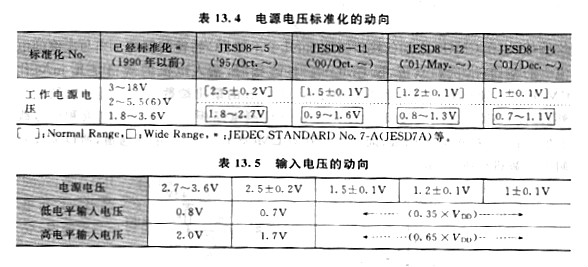

從這種市場意向和半導體廠家的高集成度、高附加值兩個角度看,都請求器件的微細化、低電壓化。表13.4列出了包括EIA/JEDEC依然在審議中的電源電壓范圍的規范化意向。低電壓化業已進入1.0V系電源。

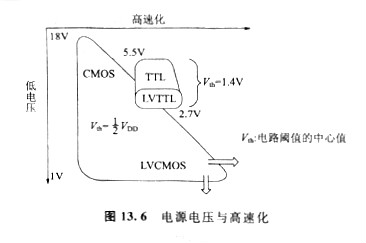

表13.5列出其輸入電壓規格(接口規格)的意向,到3.3V系(或者3.0V系)電源電壓,都是VIL=0.8V、VIH=2.0V就是說以維持TTL電平的“LVTTL”(LV:LowVoltage)作為輸入電壓規格規范,在TTL習氣運用的信息、通訊范疇運用著。不過在電源電壓進一步降低后,VIL,和VIH的規格就只能采用CMOS電平規范。 圖13.6形象地表現出電源電壓和高速化的關系。TTL運用在以5V工作為中心的高速應用范疇,3V系的應用被合適于Bi-CMOS技術的低電壓型(LVTTL)掩蓋。TTL/LVTTL的電路閾值設計大約是1.4V,輸入“L”/“H”的電壓規格是0.8V/2.0V。

CMOS在原來寬的工作電壓范圍的根底上,產生了低電壓、高速產品,也包含了TTL的性能。CMOS的電路閾值設計為1/2VDD,輸入“L”/“H”的電壓規格是0.25~0.35VDD/0.65~0.75VDD。

CMOS器件的接口以CMOS電平為規范,不過也產生適用特定用處的接口規格。最大的意向是差動傳送。這一點將在后面引見。

烜芯微專業制造二極管,三極管,MOS管,20年,工廠直銷省20%,1500家電路電器生產企業選用,專業的工程師幫您穩定好每一批產品,如果您有遇到什么需要幫助解決的,可以點擊右邊的工程師,或者點擊銷售經理給您精準的報價以及產品介紹